INSTRUMENTS

SLASEG6 – MAY 2018

# TAS3251 175-W Stereo, 350-W Mono Ultra-HD Digital-Input Class-D Amplifier with Advanced DSP Processing

### 1 Features

- Flexible Audio Inputs

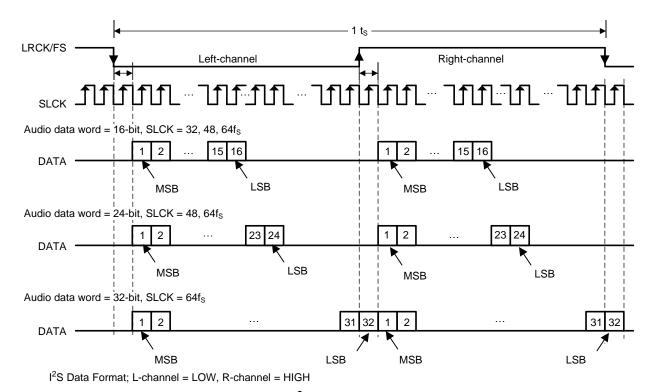

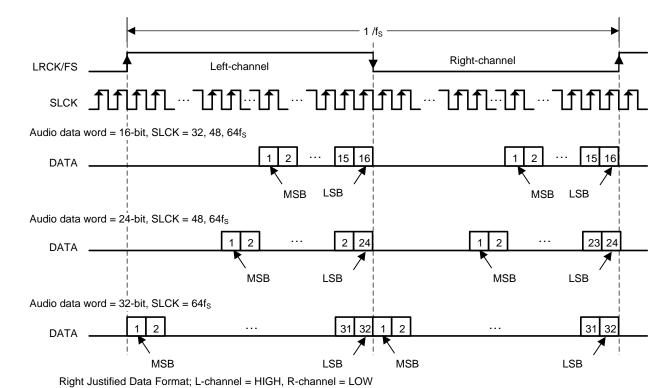

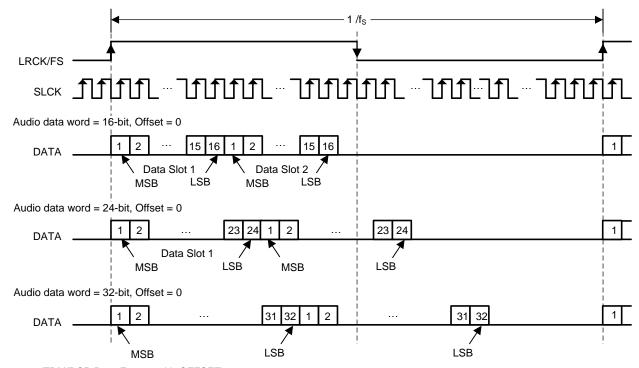

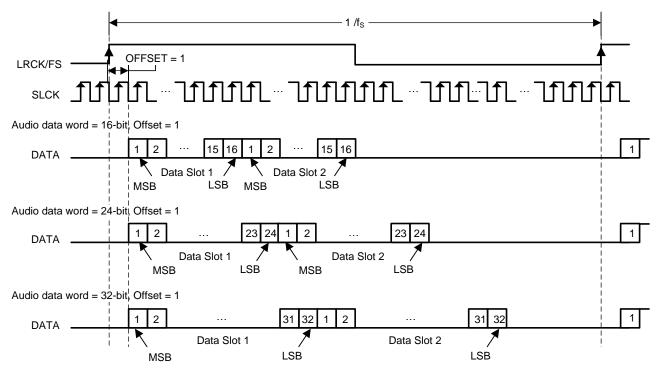

- I<sup>2</sup>S, TDM, Left-Justified, Right-Justified

- 32 kHz, 44.1 kHz, 48 kHz, 96 kHz

- Supports 3-Wire Digital Input (No MCLK)

- Total Output Power at 10% THD+N

- 175-W Stereo into 4  $\Omega$  in BTL Configuration

- 220-W Stereo into 3 Ω in BTL Configuration

- 350-W Mono into 2  $\Omega$  in PBTL Configuration

- Total Output Power at 1% THD+N

- 140-W Stereo into 4 Ω in BTL Configuration

- 175-W Stereo into 3  $\Omega$  in BTL Configuration

- 285-W Mono into 2  $\Omega$  in PBTL Configuration

- Advanced Integrated Closed-Loop Design

- Ultra Low 0.01% THD+N at 1 W into 4  $\Omega$

- <0.01% THD+N to Clipping</p>

- 60 dB PSRR (BTL, No Input Signal)

- <95 μV Output Noise (A-Weighted)</li>

- >108 dB SNR (A-Weighted)

- Fixed-Function Processing Features

- SmartEQ (15x BiQuads)

- Crossover EQ (2x 5 BiQuads)

- 3-Band Advanced DRC + AGL

- Dynamic EQ and SmartBass

- Sample Rate Conversion

- Control Features

- I<sup>2</sup>C Software Mode Control

- Address Select Pin

- 90% Efficient Class-D Operation (4 Ω)

- Wide 12-V to 36-V Supply Voltage Operation

- Integrated Protection with Error Reporting: Undervoltage, Cycle-by-cycle Current Limit, Short Circuit, Clipping detection, Overtemperature Warning and Shutdown and DC Speaker Protection

### 2 Applications

- · Bluetooth and WiFi Speakers

- Soundbars

- Subwoofers

- · Bookshelf Stereo Systems

- Professional and Public Address (PA) Speakers

- Active Crossover and Two-Way Speakers

### 3 Description

TAS3251 is a digital-input, high-performance Class-D audio amplifier that enables true premium sound quality with Class-D efficiency. The digital front-end features a high-performance Burr-Brown™ DAC with integrated DSP for advanced audio processing, including SmartAmp and SmartEQ. The first highpower single-chip solution reduces overall system solution size and cost. The DSP is supported by TI PurePath™ Console Graphical tuning software for quick and easy speaker tuning and control. The Class-D power stage features advanced integrated feedback and proprietary high-speed gate drive error correction for ultra-low distortion and noise across the audio band. The device operates in AD-mode and can drive up to 2 x 175 W into 4  $\Omega$  load and 2 x 220 W into 3  $\Omega$  load.

### **Device Information**

| PART NUMBER | PACKAGE    | BODY SIZE (NOM)    |

|-------------|------------|--------------------|

| TAS3251     | HSSOP (56) | 18.41 mm × 7.49 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

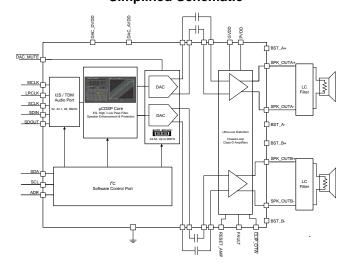

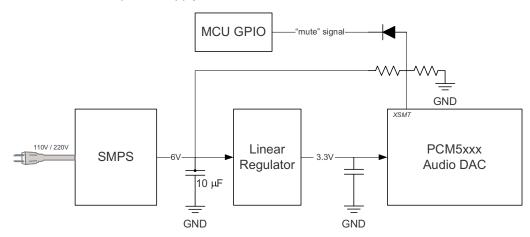

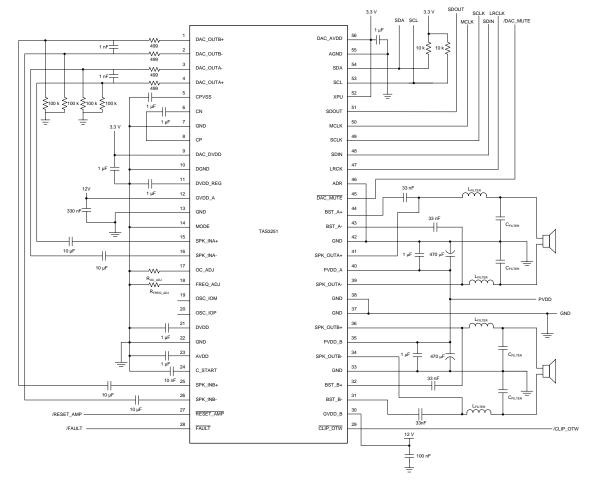

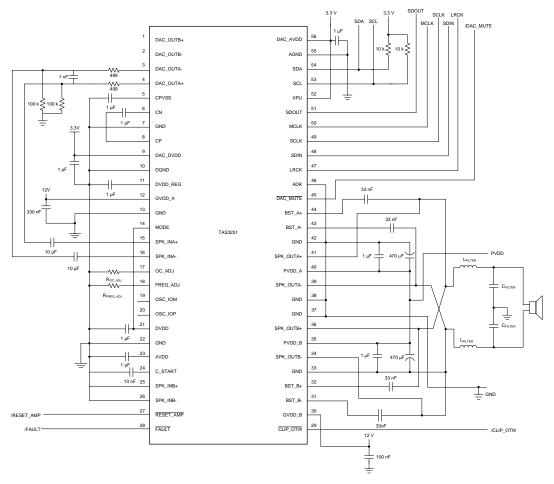

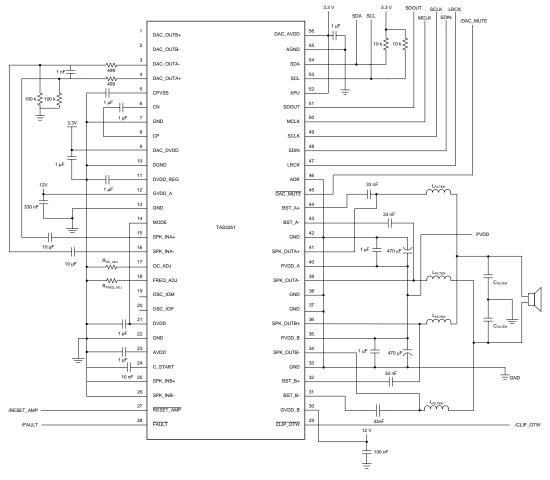

### **Simplified Schematic**

### **Table of Contents**

| 1 | Features 1                                  | 8  | Detailed Description                 | 21               |

|---|---------------------------------------------|----|--------------------------------------|------------------|

| 2 | Applications 1                              |    | 8.1 Overview                         | 21               |

| 3 | Description 1                               |    | 8.2 Functional Block Diagram         | 21               |

| 4 | Revision History2                           |    | 8.3 Feature Description              | 22               |

| 5 | Device Comparison Table                     |    | 8.4 Device Functional Modes          | <mark>5</mark> 1 |

| 6 | Pin Configuration and Functions4            |    | 8.5 Programming                      | 53               |

| - | _                                           |    | 8.6 Register Maps                    | 64               |

| 7 | Specifications7                             | 9  | Application and Implementation       | 101              |

|   | 7.1 Absolute Maximum Ratings                |    | 9.1 Typical Applications             |                  |

|   | 7.2 ESD Ratings                             | 10 | Power Supply Recommendations         |                  |

|   | 7.3 Recommended Operating Conditions        |    | 10.1 Power Supplies                  |                  |

|   | 7.4 Thermal Information                     | 11 | Layout                               |                  |

|   | 7.5 Amplifier Electrical Characteristics    |    | -                                    |                  |

|   | 7.6 DAC Electrical Characteristics 11       |    | ,                                    |                  |

|   | 7.7 Audio Characteristics (BTL) 12          |    | 11.2 Layout Examples                 |                  |

|   | 7.8 Audio Characteristics (PBTL)            | 12 | Device and Documentation Support     | 115              |

|   | 7.9 MCLK Timing                             |    | 12.1 Device Support                  | 115              |

|   | 7.10 Serial Audio Port Timing – Slave Mode  |    | 12.2 Community Resources             | 116              |

|   | 7.11 Serial Audio Port Timing – Master Mode |    | 12.3 Trademarks                      | 116              |

|   | 7.12 I <sup>2</sup> C Bus Timing –Standard  |    | 12.4 Electrostatic Discharge Caution | 116              |

|   | 7.13 I <sup>2</sup> C Bus Timing —Fast      |    | 12.5 Glossary                        |                  |

|   | 7.14 Timing Diagrams                        | 13 | Mechanical, Packaging, and Orderable |                  |

|   | 7.14 Tirling Diagrams                       | .5 | Information                          | 116              |

### 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| DATE     | REVISION | NOTES            |

|----------|----------|------------------|

| May 2018 | *        | Initial release. |

## 5 Device Comparison Table

| DEVICE NAME | DESCRIPTION                                                                                    | AUDIO INPUT<br>INTERFACE | PAD<br>LOCATION |

|-------------|------------------------------------------------------------------------------------------------|--------------------------|-----------------|

| TAS3251     | 175-W Stereo, 350-W Mono Ultra-HD Digital-Input Class-D Amplifier with Advanced DSP Processing | Digital                  | Тор             |

| TAS3245     | 115-W Stereo, 230-W Mono Ultra-HD Digital-Input Class-D Amplifier with Advanced DSP Processing | Digital                  | Тор             |

| TAS5782M    | 30-W Stereo, 60-W Mono Digital-Input Class-D Amplifier with Advanced DSP Processing            | Digital                  | Bottom          |

| TPA3244     | 60-W Stereo, 100-W Peak Ultra-HD Pad-Down Class-D Amplifier                                    | Analog                   | Bottom          |

| TPA3245     | 115-W Stereo, 230-W Mono Ultra-HD Analog-Input Class-D Amplifier                               | Analog                   | Тор             |

| TPA3250     | 70-W Stereo, 130-W Peak Ultra-HD Pad-Down Class-D Amplifier                                    | Analog                   | Bottom          |

| TPA3251     | 175-W Stereo, 350-W Mono Ultra-HD Analog-Input Power Stage                                     | Analog                   | Тор             |

| TPA3255     | 315-W Stereo, 600-W Mono Ultra-HD Analog-Input Class-D Amplifier                               | Analog                   | Тор             |

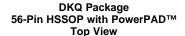

### 6 Pin Configuration and Functions

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

### **Pin Functions**

|     | PIN (a)   |                     |                                                                                                                                                                                                                                                                                                                                             |  |  |

|-----|-----------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NO. | NAME      | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                 |  |  |

| 1   | DAC_OUTB+ | 0                   | Differential DAC output B+.                                                                                                                                                                                                                                                                                                                 |  |  |

| 2   | DAC_OUTB- | 0                   | Differential DAC output B                                                                                                                                                                                                                                                                                                                   |  |  |

| 3   | DAC_OUTA- | 0                   | Differential DAC output A                                                                                                                                                                                                                                                                                                                   |  |  |

| 4   | DAC_OUTA+ | 0                   | Differential DAC output A+.                                                                                                                                                                                                                                                                                                                 |  |  |

| 5   | CPVSS     | Р                   | $-3.3$ V negative charge pump supply output for DAC. Connect 1 $\mu\text{F}$ ceramic capacitor to GND. Refer to section Power Supply Recommendations                                                                                                                                                                                        |  |  |

| 6   | CN        | Р                   | Negative pin for capacitor connection used in the line-driver charge pump. Connect 1 μF ceramic capacitor from CN to CP. Refer to section: Power Supply Recommendations                                                                                                                                                                     |  |  |

| 7   | GND       | G                   | Ground pin for device.                                                                                                                                                                                                                                                                                                                      |  |  |

| 8   | СР        | Р                   | Positive pin for capacitor connection used in the line-driver charge pump. Connect 1 µF capacitor from CN to CP. Refer to section: Power Supply Recommendations                                                                                                                                                                             |  |  |

| 9   | DAC_DVDD  | Р                   | DAC power supply input for digital logic and charge pump. Connect 3.3 V and a 1 uF ceramic capacitor to GND. Refer to section: DAC_DVDD and DAC_AVDD Supplies                                                                                                                                                                               |  |  |

| 10  | DGND      | G                   | Ground reference for digital circuitry. Connect this pin to the system ground.                                                                                                                                                                                                                                                              |  |  |

| 11  | DVDD_REG  | Р                   | DAC voltage regulator output derived from DAC_DVDD supply for use for internal digital circuitry (1.8 V). This pin is provided as a connection point for filtering capacitors for this supply and must not be used to power any external circuitry. Connect 1 µF ceramic capacitor to GND. Refer to section: DAC_DVDD and DAC_AVDD Supplies |  |  |

| 12  | GVDD_A    | Р                   | Gate drive supply input for amplifier channel A. Connect 12 V and a 0.1 µF capacitor to GND. Refer to section: GVDD_X Supply                                                                                                                                                                                                                |  |  |

| 13  | GND       | G                   | Ground pin for device.                                                                                                                                                                                                                                                                                                                      |  |  |

| 14  | MODE      | I                   | Output configuration mode selection. BTL = 0, PBTL = 1. Refer to table: Mode Selection Pins                                                                                                                                                                                                                                                 |  |  |

| 15  | SPK_INA+  | ļ                   | Input signal for half-bridge A+.                                                                                                                                                                                                                                                                                                            |  |  |

| 16  | SPK_INA-  | l                   | Input signal for half-bridge A                                                                                                                                                                                                                                                                                                              |  |  |

| 17  | OC_ADJ    | 1/0                 | Over-Current threshold programming pin. Refer to section: Overload and Short Circuit Current Protection                                                                                                                                                                                                                                     |  |  |

| 18  | FREQ_ADJ  | 1/0                 | Oscillator frequency programming pin. Refer to section: Oscillator for Output Power Stage                                                                                                                                                                                                                                                   |  |  |

| 19  | OSC_IOM   | 1/0                 | PWM switching oscillator synchronization interface. Optional. Do not connect if unused. Refer to section: Oscillator Synchronization and Slave Mode                                                                                                                                                                                         |  |  |

| 20  | OSC_IOP   | 0                   | PWM switching oscillator synchronization interface. Optional. Do not connect if unused. Refer to section: Oscillator Synchronization and Slave Mode                                                                                                                                                                                         |  |  |

| 21  | DVDD      | Р                   | Internal voltage regulator, amplifier digital section. Connect 1 µF ceramic capacitor to GND. Refer to section: VDD Supply                                                                                                                                                                                                                  |  |  |

| 22  | GND       | G                   | Ground pin for device.                                                                                                                                                                                                                                                                                                                      |  |  |

| 23  | AVDD      | Р                   | Internal voltage regulator, amplifier analog section. Connect 1 µF ceramic capacitor to GND. Refer to section: VDD Supply                                                                                                                                                                                                                   |  |  |

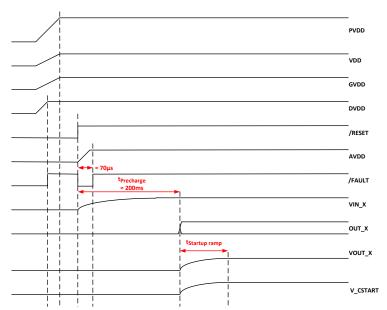

| 24  | C_START   | 0                   | Startup ramp, requires a charging capacitor to GND. Connect 10 nF to GND for best pop prevention. Refer to section: Pop and Click Free Startup and Shutdown                                                                                                                                                                                 |  |  |

| 25  | SPK_INB+  | I                   | Input signal for half-bridge B+.                                                                                                                                                                                                                                                                                                            |  |  |

| 26  | SPK_INB-  | I                   | Input signal for half-bridge B                                                                                                                                                                                                                                                                                                              |  |  |

| 27  | RESET_AMP | I                   | Device reset, active low. Use for amplifier reset and mute. Refer to section: Output Power Stage Reset                                                                                                                                                                                                                                      |  |  |

| 28  | FAULT     | 0                   | Shutdown signal, open drain; active low. Internal pull-up resistor to DVDD. Do not connect if unused. Refer to section: Device Output Stage Protection System                                                                                                                                                                               |  |  |

| 29  | CLIP_OTW  | 0                   | Clipping warning and over-temperature warning; open drain; active low. Internal pull-up resistor to DVDD. Do not connect if unused. Refer to section: Device Output Stage Protection System                                                                                                                                                 |  |  |

| 30  | GVDD_B    | Р                   | Gate drive supply input for amplifier channel B. Connect 12 V and a 0.1 µF capacitor to GND. Refer to section: GVDD_X Supply                                                                                                                                                                                                                |  |  |

| 31  | BST_B-    | Р                   | HS bootstrap supply (BST), external 0.033 μF capacitor to SPK_OUTB Refer to section: BST Supply                                                                                                                                                                                                                                             |  |  |

| 32  | BST_B+    | Р                   | HS bootstrap supply (BST), external 0.033 μF capacitor to SPK_OUTB+. Refer to section: BST Supply                                                                                                                                                                                                                                           |  |  |

| 33  | GND       | G                   | Ground pin for device.                                                                                                                                                                                                                                                                                                                      |  |  |

| 34  | SPK_OUTB- | 0                   | Output, half bridge B                                                                                                                                                                                                                                                                                                                       |  |  |

| 35  | PVDD_B    | Р                   | PVDD supply for channel B. Connect large bulk capacitor and 1 µF ceramic decoupling capacitor to GND and place near pin. Refer to section: PVDD Supply                                                                                                                                                                                      |  |  |

| 36  | SPK_OUTB+ | 0                   | Output, half bridge B+.                                                                                                                                                                                                                                                                                                                     |  |  |

| 37  | GND       | G                   | Ground pin for device.                                                                                                                                                                                                                                                                                                                      |  |  |

| 38  | GND       | G                   | Ground pin for device.                                                                                                                                                                                                                                                                                                                      |  |  |

|     |           |                     |                                                                                                                                                                                                                                                                                                                                             |  |  |

### (1) I=Input, O=Output, I/O= Input/Output, P=Power, G=Ground

### Pin Functions (continued)

| PIN |           | <b>-</b> >(1)       |                                                                                                                                                                                                                                                                                          |  |  |  |

|-----|-----------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NO. | NAME      | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                              |  |  |  |

| 39  | SPK_OUTA- | 0                   | Output, half bridge A                                                                                                                                                                                                                                                                    |  |  |  |

| 40  | PVDD_A    | Р                   | DD supply for channel A. Connect large bulk capacitor and 1 µF ceramic decoupling capacitor to GND and the near pin. Refer to section: PVDD Supply                                                                                                                                       |  |  |  |

| 41  | SPK_OUTA+ | 0                   | Output, half bridge A+.                                                                                                                                                                                                                                                                  |  |  |  |

| 42  | GND       | G                   | Ground pin for device.                                                                                                                                                                                                                                                                   |  |  |  |

| 43  | BST_A-    | Р                   | HS bootstrap supply (BST), external 0.033 μF capacitor to SPK_OUTA Refer to section: BST Supply                                                                                                                                                                                          |  |  |  |

| 44  | BST_A+    | Р                   | HS bootstrap supply (BST), external 0.033 μF capacitor to SPK_OUTA+. Refer to section: BST Supply                                                                                                                                                                                        |  |  |  |

| 45  | DAC_MUTE  | I                   | Hardware controlled DAC mute function. Pull low (connected to DGND) to mute the device and pull high (connected to DAC_DVDD) to unmute the device. Refer to section: Mute with DAC_MUTE or Clock Error                                                                                   |  |  |  |

| 46  | ADR       | 1                   | Sets the LSB of the I <sup>2</sup> C address to 0 if pulled to GND, to 1 if pulled to DAC_DVDD. Refer to table: Slave Address Select                                                                                                                                                     |  |  |  |

| 47  | LRCK      | I                   | Left-Right Word (I <sup>2</sup> S) or Frame (TDM) select clock for digital audio signal. In I <sup>2</sup> S, LJ, and RJ, this corresponds to the left channel and right channel boundary. In TDM mode, this corresponds to the frame sync boundary. Refer to section: Serial Audio Port |  |  |  |

| 48  | SDIN      | I                   | Audio data serial port, data in. Refer to section: Serial Audio Port                                                                                                                                                                                                                     |  |  |  |

| 49  | SCLK      | I                   | Serial or bit clock for the digital signal that is active on the input data line of the serial data port. Refer to section: Serial Audio Port                                                                                                                                            |  |  |  |

| 50  | MCLK      | I                   | Master clock used for internal clock tree and sub-circuit and state machine clocking. Refer to section: Serial Audio Port                                                                                                                                                                |  |  |  |

| 51  | SDOUT     | 1/0                 | Audio data serial port, data output. Refer to section: SDOUT Port and Hardware Control Pin                                                                                                                                                                                               |  |  |  |

| 52  | XPU       | I                   | External pull-up, logic level pin. For normal operation, this pin should be connected directly to 3.3 V (DAC_DVDD or DAC_AVDD).                                                                                                                                                          |  |  |  |

| 53  | SCL       | I                   | I <sup>2</sup> C serial control port clock. Refer to section: I2C Communication Port                                                                                                                                                                                                     |  |  |  |

| 54  | SDA       | 1/0                 | I <sup>2</sup> C serial control port data. Refer to section: I2C Communication Port                                                                                                                                                                                                      |  |  |  |

| 55  | AGND      | G                   | Ground reference for analog circuitry. Connect to system ground.                                                                                                                                                                                                                         |  |  |  |

| 56  | DAC_AVDD  | Р                   | DAC power supply input for DAC internal analog circuitry. Connect 3.3 V and a 1 uF ceramic capacitor to GND. Refer to section: DAC_DVDD and DAC_AVDD Supplies                                                                                                                            |  |  |  |

|     | PowerPAD™ | G                   | Ground, connect to grounded heat sink.                                                                                                                                                                                                                                                   |  |  |  |

### **Table 1. Mode Selection Pins**

| Output<br>Configuration | Input Mode | MODE Pin | SPK_INB+<br>Pin | SPK_INB- Pin | Description                                                                                                                 |

|-------------------------|------------|----------|-----------------|--------------|-----------------------------------------------------------------------------------------------------------------------------|

| 2 x BTL                 | 2N + 1     | 0        | X               | X            | Stereo BTL output configuration                                                                                             |

| 1 x PBTL                | 2N + 1     | 1        | 0               | 0            | Paralleled BTL configuration pre-filter or post-filter. Connect SPK_INB+ and INPUT_B- to GND with no DC blocking capacitor. |

### Table 2. I<sup>2</sup>C Device Slave Address

| ADR Pin |                           | Hex  | Binary    |

|---------|---------------------------|------|-----------|

|         | 7-bit Address             | 0x4A | 1001 010  |

| 0       | 7-bit Address + Write Bit | 0x94 | 1001 0100 |

|         | 7-bit Address + Read Bit  | 0x95 | 1001 0101 |

|         | 7-bit Address             | 0x4B | 1001 011  |

| 1       | 7-bit Address + Write Bit | 0x96 | 1001 0110 |

|         | 7-bit Address + Read Bit  | 0x97 | 1001 0111 |

### 7 Specifications

### 7.1 Absolute Maximum Ratings

Free-air room temperature 25°C (unless otherwise noted) (1)

|                        |                                                                                       | MIN  | MAX                         | UNIT |

|------------------------|---------------------------------------------------------------------------------------|------|-----------------------------|------|

|                        | PVDD_X to GND <sup>(2)</sup>                                                          | -0.3 | 50                          | V    |

|                        | BST_X to GVDD_X <sup>(2)</sup>                                                        | -0.3 | 50                          | V    |

|                        | BST_X to GND <sup>(2)</sup>                                                           | -0.3 | 62.5                        | V    |

| Cumply Voltage         | VDD to GND                                                                            | -0.3 | 13.2                        | V    |

| Supply Voltage         | GVDD_X to GND <sup>(2)</sup>                                                          | -0.3 | 13.2                        | V    |

|                        | DVDD to GND                                                                           | -0.3 | 4.2                         | V    |

|                        | AVDD to GND                                                                           | -0.3 | 8.5                         | V    |

|                        | DAC_DVDD, DAC_AVDD                                                                    | -0.3 | 3.9                         | V    |

| Analag Interface Dina  | SPK_OUTX to GND <sup>(2)</sup>                                                        | -0.3 | 50                          | V    |

| Analog Interface Pins  | SPK_INX to GND                                                                        | -0.3 | 7                           | V    |

|                        | OC_ADJ, MODE, OSC_IOP, OSC_IOM, FREQ_ADJ, C_START to GND                              | -0.3 | 4.2                         | V    |

| Digital Interface Dina | RESET_AMP, FAULT, CLIP_OTW to GND                                                     | -0.3 | 4.2                         | V    |

| Digital Interface Pins | Continuous sink current RESET_AMP, FAULT, CLIP_OTW to GND                             |      | 9                           | mA   |

|                        | ADR, $\overline{\rm DAC\_MUTE}$ , LRCK, MCLK, SCL, SCLK, SDA, SDIN, SDOUT, XPU to GND | -0.5 | V <sub>DAC_DVDD</sub> + 0.5 | V    |

| т                      | Operating junction temperature range, power die                                       | -40  | 165                         | °C   |

| TJ                     | Operating junction temperature, digital die                                           | -40  | 125                         | °C   |

| T <sub>stg</sub>       | Storage temperature range                                                             | -40  | 150                         | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions forextended periods may affect device reliability.

### 7.2 ESD Ratings

|                    |               |                                                                     | VALUE | UNIT |

|--------------------|---------------|---------------------------------------------------------------------|-------|------|

| \/                 | Electrostatic | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>   | ±2000 | \/   |

| V <sub>(ESD)</sub> | discharge     | Charged-device model (CDM), per JEDEC specification JESD22-C101 (2) | ±500  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 2000-V HBM allows safemanufacturing with a standard ESD control process.

<sup>(2)</sup> These voltages represents the DC voltage + peak AC waveformmeasured at the terminal of the device in all conditions...

<sup>(2)</sup> JEDEC document JEP157 states that 500-V CDM allows safemanufacturing with a standard ESD control process.

### 7.3 Recommended Operating Conditions

Free-air room temperature 25°C (unless otherwise noted)

|                          |                                                                                              |                                 | MIN                            | TYP | MAX                            | UNIT |

|--------------------------|----------------------------------------------------------------------------------------------|---------------------------------|--------------------------------|-----|--------------------------------|------|

| PVDD_X                   | Half-bridge supply                                                                           | DC supply voltage               | 12                             | 36  | 38                             | V    |

| GVDD_X                   | Supply for logic regulators and gate-drive circuitry                                         | DC supply voltage               | 10.8                           | 12  | 13.2                           | V    |

| VDD                      | Digital regulator supply voltage                                                             | DC supply voltage               | 10.8                           | 12  | 13.2                           | V    |

| DAC_AVDD                 | Power supply for DAC internal analog circuitry.                                              | DC supply voltage               | 2.9                            | 3.3 | 3.63                           | V    |

| DAC_DVDD <sup>(1)</sup>  | DAC digital power supply and power supply for charge pump                                    | DC supply voltage               | 2.9                            | 3.3 | 3.63                           | V    |

| R <sub>L</sub> (BTL)     | ldid                                                                                         | Output filter inductance within | 2.7                            | 4   |                                | 0    |

| R <sub>L</sub> (PBTL)    | Load impedance                                                                               | recommended value range         | 1.6                            | 2   |                                | Ω    |

| L <sub>OUT</sub> (BTL)   |                                                                                              | Minimum output inductance at    | 5                              |     |                                |      |

| L <sub>OUT</sub> (PBTL)  | Output filter inductance                                                                     | IOC                             | 5                              |     |                                | μН   |

|                          | PWM frame resistor tolerance selectable for AM interference avoidance; 1% Resistor tolerance | Nominal                         | 575                            | 600 | 625                            | kHz  |

| F <sub>PWM</sub>         |                                                                                              | AM1                             | 475                            | 500 | 525                            |      |

|                          |                                                                                              | AM2                             | 430                            | 450 | 470                            |      |

|                          |                                                                                              | Nominal; Master mode            | 9.9                            | 10  | 10.1                           |      |

| $R_{(FREQ\_ADJ)}$        | PWM frame rate programming resistor                                                          | AM1; Master mode                | 19.8                           | 20  | 20.2                           | kΩ   |

|                          |                                                                                              | AM2; Master mode                | 29.7                           | 30  | 30.3                           |      |

| C <sub>PVDD</sub>        | PVDD close decoupling capacitors                                                             |                                 | 1.0                            |     |                                | μF   |

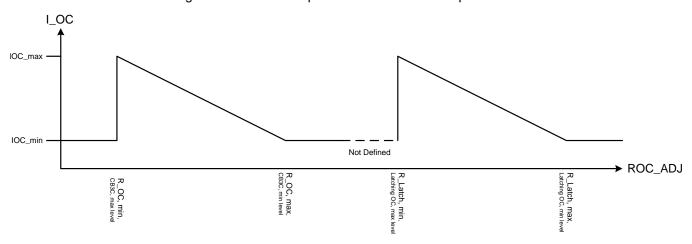

| R <sub>OC</sub>          | Over-current programming resistor                                                            | Resistor tolerance = 5%         | 22                             |     | 30                             | kΩ   |

| R <sub>OC(LATCHED)</sub> | Over-current programming resistor                                                            | Resistor tolerance = 5%         | 47                             |     | 64                             | kΩ   |

| $V_{(FREQ\_ADJ)}$        | Voltage on FREQ_ADJ pin for slave mode operation                                             | Slave mode                      |                                | 3.3 |                                | V    |

| $V_{IH(DigIn)}$          | Input logic high for DAC_DVDD referenced digital inputs (1) (2)                              |                                 | 0.9 ×<br>V <sub>DAC_DVDD</sub> |     | V <sub>DAC_DVDD</sub>          | V    |

| $V_{IL(DigIn)}$          | Input logic low for DAC_DVDD referenced digital inputs (1) (3)                               |                                 | V <sub>DAC_DVDD</sub>          | 0   | 0.1 x<br>V <sub>DAC_DVDD</sub> | V    |

| T <sub>J</sub>           | Junction temperature                                                                         |                                 | 0                              |     | 125                            | °C   |

- DAC\_DVDD referenced digital pins include: ADR, LRCK, MCLK, \(\overline{DAC\_MUTE}\), SCL, SCLK, SDA, SDIN, SDOUT and XPU. Front-end (DAC and DSP) pins should be referenced to DAC\_DVDD. Power stage digital pins should be referenced to DVDD.

- All TAS3251 ground pins should be referenced to the system ground.

### 7.4 Thermal Information

|                      |                                              | TAS3251                        |      |

|----------------------|----------------------------------------------|--------------------------------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | DKQ 56-PIN (HSSOP)             | UNIT |

|                      | THERMAL METRO                                | JEDEC STANDARD 4-<br>LAYER PCB | O.W. |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 47.8                           | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 0.3                            | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 24.2                           | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 0.2                            | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 20.6                           | °C/W |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | n/a                            | °C/W |

(1) For more information about traditional and new thermalmetrics, see the Semiconductor and ICPackage Thermal Metrics application report.

**NSTRUMENTS**

# 7.5 Amplifier Electrical Characteristics

$PVDD_X = 36 \text{ V}$ ,  $GVDD_X = 12 \text{ V}$ , VDD = 12 V,  $T_C$  (Case temperature) = 75°C,  $f_S = 600 \text{ kHz}$ , unless otherwise specified.

|                                    | PARAMETER                                                 | TEST CONDITIONS                                                                           | MIN  | TYP      | MAX  | UNIT |

|------------------------------------|-----------------------------------------------------------|-------------------------------------------------------------------------------------------|------|----------|------|------|

| AMPLIFIER INTERNA                  | L VOLTAGE REGULATOR AND CURRE                             | ENT CONSUMPTION                                                                           |      |          |      |      |

| DVDD                               | Voltage regulator for internal use                        | VDD = 12 V                                                                                | 3    | 3.3      | 3.6  | V    |

| AVDD                               | Voltage regulator for internal use                        | VDD = 12 V                                                                                |      | 7.8      |      | V    |

|                                    |                                                           | 50% duty cycle                                                                            |      | 90       |      | mA   |

| I <sub>GVDD_A + GVDD_B + VDD</sub> | GVDD and VDD supply current                               | Reset mode                                                                                |      | 19       |      | mA   |

|                                    |                                                           | 50% duty cycle with recommended                                                           |      |          |      |      |

| I <sub>PVDD X</sub>                | PVDD idle current                                         | output filter                                                                             |      | 20       |      | mA   |

|                                    |                                                           | Reset mode, no switching                                                                  |      | 0.0048   |      | mA   |

| ANALOG INPUTS                      |                                                           |                                                                                           |      |          |      |      |

| R <sub>IN</sub>                    | Input resistance                                          |                                                                                           |      | 24       |      | kΩ   |

| V <sub>IN</sub>                    | Maximum input voltage swing, SPK_INx pins                 |                                                                                           |      | 7        |      | V    |

| I <sub>IN</sub>                    | Maximum input current, SPK_INx pins                       |                                                                                           |      | 1        |      | mA   |

| G                                  | Inverting voltage gain                                    | Amplifier VOUT/VIN                                                                        |      | 20       |      | dB   |

| AMPLIFIER OSCILLA                  |                                                           | 1                                                                                         |      |          |      | 1    |

|                                    | Nominal, Master Mode                                      | F <sub>PWM</sub> × 6                                                                      | 3.45 | 3.6      | 3.75 | MHz  |

| f <sub>OSC(IO+)</sub>              | AM1, Master Mode                                          | F <sub>PWM</sub> × 6                                                                      | 2.85 | 3        | 3.15 | MHz  |

| U3U(IU+)                           | AM2, Master Mode                                          | F <sub>PWM</sub> × 6                                                                      | 2.58 | 2.7      | 2.82 | MHz  |

| V <sub>IH</sub>                    | High level input voltage                                  | I PWM X C                                                                                 | 1.86 | <b>L</b> | 2.02 | V    |

| V <sub>IL</sub>                    | Low level input voltage                                   |                                                                                           | 1.00 |          | 1.45 | V    |

| <u>VIL</u><br>OUTPUT-STAGE MOS     |                                                           |                                                                                           |      |          | 1.40 | V    |

| OUTFUT-STAGE MUS                   | Drain-to-source resistance, low-side                      | T <sub>1</sub> = 25°C, Includes metallization                                             |      |          |      |      |

| R <sub>DS(on)</sub>                | (LS)                                                      | resistance, GVDD = 12 V                                                                   |      | 60       | 100  | mΩ   |

|                                    |                                                           |                                                                                           | 60   | 100      | mΩ   |      |

| AMPLIFIER I/O PROT                 | ECTION                                                    |                                                                                           |      |          |      |      |

| $V_{uvp,VDD,GVDD}$                 | Undervoltage protection limit, GVDD_X and VDD             |                                                                                           |      | 9.5      |      | V    |

| $V_{uvp,VDD,\;GVDD,hyst}$          | Undervoltage protection hysteresis, GVDD_X and VDD        |                                                                                           |      | 0.6      |      | V    |

| OTW                                | Over-temperature warning, CLIP_OTW (1)                    |                                                                                           | 115  | 125      | 135  | °C   |

| OTW <sub>hyst</sub>                | Temperature drop required to remove OTW event on CLIP_OTW |                                                                                           |      | 25       |      | °C   |

| OTE                                | Over-temperature error                                    |                                                                                           | 145  | 155      | 165  | °C   |

| OTE-OTW <sub>(differential)</sub>  | OTE - OTW differential                                    |                                                                                           |      | 30       |      | °C   |

| OTE <sub>hyst</sub>                | A reset is required to clear an OTE event                 |                                                                                           |      | 25       |      | °C   |

| OLPC                               | Overload protection counter for CB3C mode                 | F <sub>PWM</sub> = 600 kHz (1024 PWM cycles for all F <sub>PWM</sub> )                    |      | 1.7      |      | ms   |

| loc                                | Overcurrent limit for CB3C mode                           | Resistor – programmable, nominal peak current in $1\Omega$ load, $R_{OCP}$ = 22 $k\Omega$ |      | 14       |      | А    |

| I <sub>OC(LATCHED)</sub>           | Overcurrent limit for latched mode                        | Resistor – programmable, peak current in 1 $\Omega$ load, R <sub>OCP</sub> = 47k $\Omega$ |      | 14       |      | А    |

| I <sub>DCspkr</sub>                | DC speaker protection current threshold                   | BTL current imbalance threshold                                                           |      | 1.5      |      | А    |

| Гост                               | Overcurrent response time                                 | Time from switching transition to flip-state induced by overcurrent                       |      | 150      |      | ns   |

| I <sub>PD</sub>                    | Output pulldown current of each half-<br>bridge           | Connected when RESET is active to provide bootstrap charge                                |      | 3        |      | mA   |

<sup>(1)</sup> Specified by design.

Submit Documentation Feedback

Product Folder Links: TAS3251

### **Amplifier Electrical Characteristics (continued)**

$PVDD_X = 36 \text{ V}$ ,  $GVDD_X = 12 \text{ V}$ , VDD = 12 V,  $T_C$  (Case temperature) = 75°C,  $f_s = 600 \text{ kHz}$ , unless otherwise specified.

|                                         | PARAMETER                                                   | TEST CONDITIONS                   | MIN | TYP | MAX | UNIT    |  |  |

|-----------------------------------------|-------------------------------------------------------------|-----------------------------------|-----|-----|-----|---------|--|--|

| AMPLIFIER STATIC DIGITAL SPECIFICATIONS |                                                             |                                   |     |     |     |         |  |  |

| V <sub>IH</sub>                         | High-level input voltage                                    | MODE, OSC_IOP, OSC_IOM, RESET_AMP | 1.9 |     |     | V       |  |  |

| V <sub>IL</sub>                         | Low-level input voltage                                     | MODE, OSC_IOP, OSC_IOM, RESET_AMP |     |     | 0.8 | V       |  |  |

| I <sub>lkg</sub>                        | Input leakage current                                       | MODE, OSC_IOP, OSC_IOM, RESET_AMP |     |     | 100 | μΑ      |  |  |

| AMPLIFIER OTW/S                         | SHUTDOWN (FAULT)                                            |                                   |     |     |     |         |  |  |

| R <sub>INT_PU</sub>                     | Internal pullup resistance, CLIP_OTW to DVDD, FAULT to DVDD |                                   | 20  | 26  | 32  | kΩ      |  |  |

| V <sub>OH</sub>                         | High-level output voltage                                   | Internal pullup resistor          | 3   | 3.3 | 3.6 | V       |  |  |

| V <sub>OL</sub>                         | Low-level output voltage                                    | IO = 4 mA                         |     | 200 | 500 | mV      |  |  |

| Device fanout                           | CLIP_OTW, FAULT                                             | No external pullup                |     | 30  |     | devices |  |  |

**ADVANCE INFORMATION**

### 7.6 DAC Electrical Characteristics

Free-air room temperature 25°C (unless otherwise noted)

|                          | PARAMETER                                                                             | TEST CONDITIONS                                   | MIN                            | TYP MAX | UNIT                          |

|--------------------------|---------------------------------------------------------------------------------------|---------------------------------------------------|--------------------------------|---------|-------------------------------|

| DIGITAL I/O              |                                                                                       |                                                   |                                |         |                               |

| V <sub>IH1</sub>         | Input logic high threshold for DAC_DVDD referenced digital inputs <sup>(1)</sup>      |                                                   | 70%                            |         | V <sub>DAC_DVDD</sub>         |

| V <sub>IL1</sub>         | Input logic low threshold for<br>DAC_DVDD referenced digital<br>inputs <sup>(1)</sup> |                                                   |                                | 30%     | V <sub>DAC_DVDD</sub>         |

| I <sub>IH1</sub>         | Input logic high current level for<br>DAC_DVDD referenced digital<br>input pins (1)   | $V_{IN(DigIn)} = V_{DAC\_DVDD}$                   |                                | 10      | μA                            |

| I <sub>IL1</sub>         | Input logic low current level for<br>DAC_DVDD referenced digital<br>input pins (1)    | V <sub>IN(DigIn)</sub> = 0 V                      |                                | -10     | μA                            |

| V <sub>OH(DigOut)</sub>  | Output logic high voltage level (1)                                                   | I <sub>OH</sub> = 4 mA                            | 80%                            |         | V <sub>DAC_DVDD</sub>         |

| V <sub>OL(DigOut)</sub>  | Output logic low voltage level (1)                                                    | $I_{OH} = -4 \text{ mA}$                          |                                | 22%     | V <sub>DAC_DVDD</sub>         |

| I <sup>2</sup> C CONTROI | L PORT                                                                                |                                                   |                                |         |                               |

| C <sub>L(I2C)</sub>      | Allowable load capacitance for each I <sup>2</sup> C Line                             |                                                   |                                | 400     | pF                            |

| f <sub>SCL(fast)</sub>   | Support SCL frequency                                                                 | No wait states, fast mode                         |                                | 400     | kHz                           |

| f <sub>SCL(slow)</sub>   | Support SCL frequency                                                                 | No wait states, slow mode                         |                                | 100     | kHz                           |

| $V_{NH}$                 | Noise margin at High level for<br>each connected device (including<br>hysteresis)     |                                                   | 0.2 x<br>V <sub>DAC_DVDD</sub> |         | V                             |

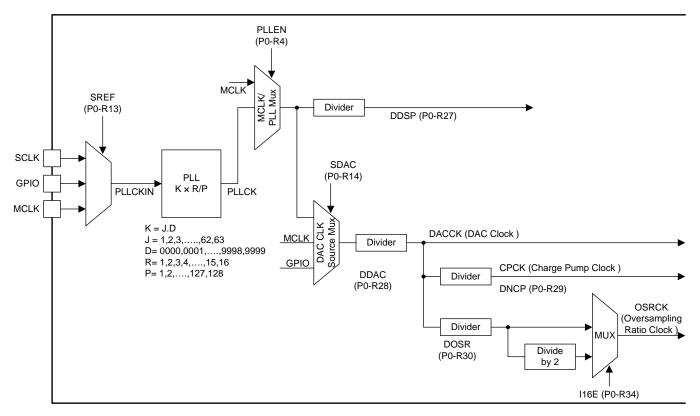

| MCLK AND P               | LL SPECIFICATIONS                                                                     |                                                   |                                |         | 1                             |

| D <sub>MCLK</sub>        | Allowable MCLK duty cycle                                                             |                                                   | 40%                            | 60%     |                               |

| f <sub>MCLK</sub>        | Supported MCLK frequencies                                                            | Up to 50 MHz                                      | 128                            | 512     | f <sub>S</sub> <sup>(2)</sup> |

|                          | DIL insult for many                                                                   | Clock divider uses fractional divide D > 0, P = 1 | 6.7                            | 20      | NAL 1-                        |

| f <sub>PLL</sub>         | PLL input frequency                                                                   | Clock divider uses integer divide D = 0, P = 1    | 1                              | 20      | - MHz                         |

| SERIAL AUD               | IO PORT                                                                               |                                                   |                                |         |                               |

| t <sub>DLY</sub>         | Required LRCK/FS to SCLK rising edge delay                                            |                                                   | 5                              |         | ns                            |

| D <sub>SCLK</sub>        | Allowable SCLK duty cycle                                                             |                                                   | 40%                            | 60%     |                               |

| f <sub>S</sub>           | Supported input sample rates                                                          |                                                   | 8                              | 96      | kHz                           |

| f <sub>SCLK</sub>        | Supported SCLK frequencies                                                            |                                                   | 32                             | 64      | f <sub>S</sub> <sup>(2)</sup> |

| f <sub>SCLK</sub>        | SCLK frequency                                                                        | Either master mode or slave mode                  |                                | 24.576  | MHz                           |

<sup>(1)</sup> DAC\_DVDD referenced digital pins include: ADR, LRCK, MCLK, DAC\_MUTE, SCL, SCLK, SDA, SDIN, SDOUT and XPU.

<sup>(2)</sup> A unit of f<sub>S</sub> indicates that the specification is the value listed in the table multiplied by the sample rate of the audio used in the TAS3251 device.

### 7.7 Audio Characteristics (BTL)

PCB and system configuration are in accordance with recommended guidelines. Audio frequency = 1 kHz, PVDD\_X = 36 V,  $GVDD\_X = 12 \text{ V}, \text{ R}_L = 4 \text{ } \Omega, \text{ f}_S = 600 \text{ kHz}, \text{ R}_{OC} = 22 \text{ k}\Omega, \text{ T}_C = 75^{\circ}\text{C}, \text{ Output Filter: } L_{DEM} = 10 \text{ } \mu\text{H}, \text{ } C_{DEM} = 1 \text{ } \mu\text{F}, \text{ } MODE = 0, \text{ } L_{DEM} = 10 \text{ } L_{DEM$ AES17 + AUX-0025 measurement filters, unless otherwise noted.

|                   | PARAMETER                                                   | TEST CONDITIONS                                            | MIN | TYP   | MAX | UNIT |  |

|-------------------|-------------------------------------------------------------|------------------------------------------------------------|-----|-------|-----|------|--|

|                   |                                                             | R <sub>L</sub> = 3 Ω, 10% THD+N                            |     | 220   |     |      |  |

| D                 | Douger output nor channel                                   | $R_L = 4 \Omega$ , 10% THD+N                               |     | 175   |     | ۱۸/  |  |

| Po                | Power output per channel                                    | $R_L = 3 \Omega$ , 1% THD+N                                |     | 175   |     | W    |  |

|                   |                                                             | $R_L = 4 \Omega$ , 1% THD+N                                |     | 140   |     |      |  |

| THD+N             | Total harmonic distortion + noise                           | 1 W                                                        |     | 0.008 |     | %    |  |

| V <sub>n</sub>    | Output integrated noise                                     | A-weighted, AES17 filter, input capacitor grounded         |     | 95    |     | μV   |  |

| Vos               | Output offset voltage                                       | Inputs AC coupled to GND                                   |     | 20    | 60  | mV   |  |

| SNR               | Signal-to-noise ratio (1)                                   |                                                            |     | 108   |     | dB   |  |

| DNR               | Dynamic range                                               |                                                            |     | 110   |     | dB   |  |

| P <sub>idle</sub> | Power dissipation due to Idle losses (I <sub>PVDD_X</sub> ) | P <sub>O</sub> = 0, 4 channels<br>switching <sup>(2)</sup> |     | 0.75  |     | W    |  |

- SNR is calculated relative to 1% THD+N outputlevel.

- Actual system idle losses also are affected by core losses of output inductors.

### 7.8 Audio Characteristics (PBTL)

PCB and system configuration are in accordance with recommended guidelines. Audio frequency = 1 kHz, PVDD\_X = 36 V,  $GVDD\_X = 12 \text{ V}, \text{ R}_L = 2 \text{ }\Omega, \text{ f}_S = 600 \text{ kHz}, \text{ R}_{OC} = 22 \text{ k}\Omega, \text{ T}_C = 75 ^{\circ}\text{C}, \text{ Output Filter: } L_{DEM} = 10 \text{ }\mu\text{H}, \text{ }C_{DEM} = 1 \text{ }\mu\text{F}, \text{ MODE} = 1, \text{ }C_{DEM} = 10 \text{ }\mu\text{H}, \text{$ outputs paralleled after LC filter, AES17 + AUX-0025 measurement filters, unlessotherwise noted.

|                   | PARAMETER                                      | TEST CONDITIONS                                                 | MIN TYP | MAX | UNIT |

|-------------------|------------------------------------------------|-----------------------------------------------------------------|---------|-----|------|

|                   |                                                | $R_L = 2 \Omega$ , 10% THD+N                                    | 355     |     |      |

|                   |                                                | $R_L = 3 \Omega$ , 10% THD+N                                    | 250     |     |      |

| Po                | Dower output per channel                       | $R_L = 4 \Omega$ , 10% THD+N                                    | 195     |     | W    |

|                   | Power output per channel                       | $R_L = 2 \Omega$ , 1% THD+N                                     | 285     |     | VV   |

|                   |                                                | $R_L = 3 \Omega$ , 1% THD+N                                     | 200     |     |      |

|                   |                                                | $R_L = 4 \Omega$ , 1% THD+N                                     | 155     |     |      |

| THD+N             | Total harmonic distortion + noise              | 1 W                                                             | 0.009   |     | %    |

| V <sub>n</sub>    | Output integrated noise                        | A-weighted, AES17 filter, input capacitor grounded 95           |         |     | μV   |

| SNR               | Signal to noise ratio <sup>(1)</sup>           | A-weighted                                                      | 108     |     | dB   |

| DNR               | Dynamic range                                  | A-weighted                                                      | 108     |     | dB   |

| P <sub>idle</sub> | Power dissipation due to idle losses (IPVDD_X) | P <sub>O</sub> = 0, 4 channels<br>switching <sup>(2)</sup> 0.75 |         |     | W    |

Product Folder Links: TAS3251

- SNR is calculated relative to 1% THD+N output level.

- Actual system idle losses are affected by core losses of output inductors.

Submit Documentation Feedback

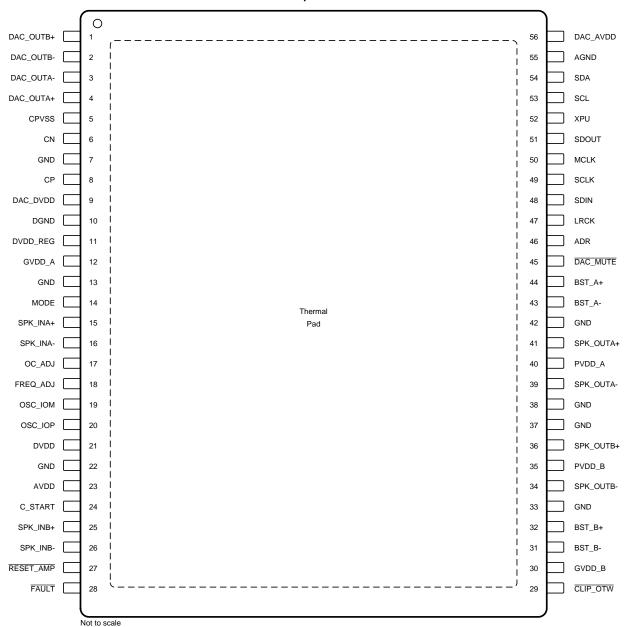

### 7.9 MCLK Timing

See Figure 1.

www.ti.com

|                    | PARAMETER              |    |      | UNIT |

|--------------------|------------------------|----|------|------|

| t <sub>MCLK</sub>  | MCLK period            | 20 | 1000 | ns   |

| t <sub>MCLKH</sub> | MCLK pulse width, high | 9  |      | ns   |

| t <sub>MCLKL</sub> | MCLK pulse width, low  | 9  |      | ns   |

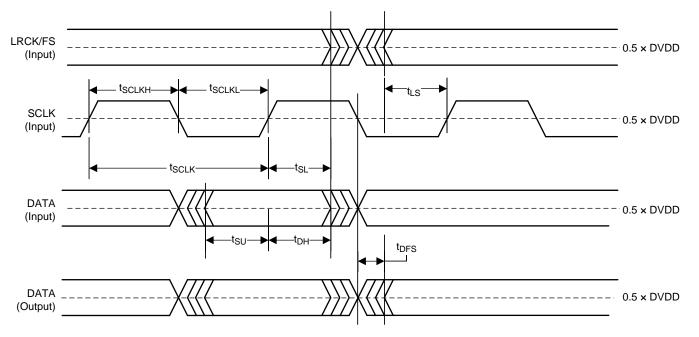

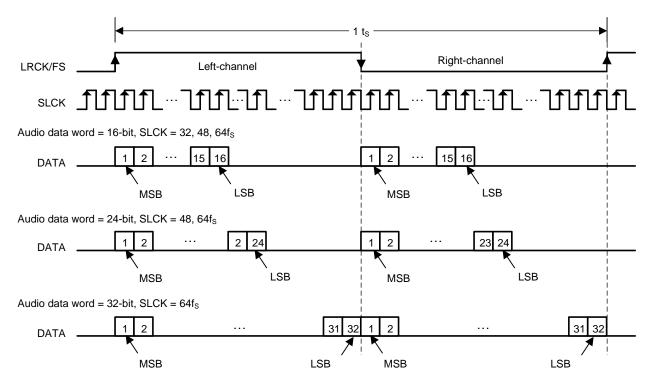

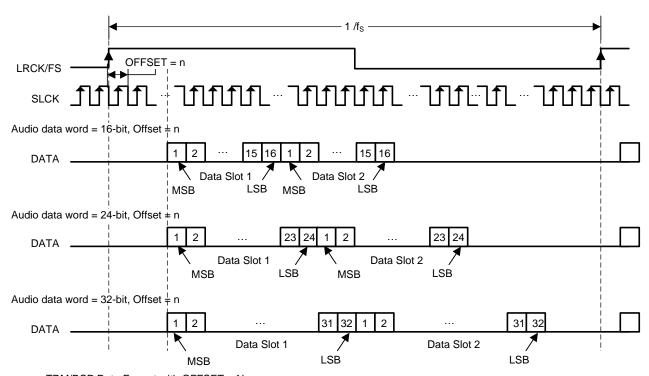

### 7.10 Serial Audio Port Timing - Slave Mode

See Figure 2.

|                    | PARAMETER                                | MIN   | MAX | UNIT |

|--------------------|------------------------------------------|-------|-----|------|

| f <sub>SCLK</sub>  | SCLK frequency                           | 1.024 |     | MHz  |

| t <sub>SCLK</sub>  | SCLK period                              | 40    |     | ns   |

| t <sub>SCLKL</sub> | SCLK pulse width, low                    | 16    |     | ns   |

| t <sub>SCLKH</sub> | SCLK pulse width, high                   | 16    |     | ns   |

| t <sub>SL</sub>    | SCLK rising to LRCK/FS edge              | 8     |     | ns   |

| t <sub>LS</sub>    | LRCK/FS Edge to SCLK rising edge         | 8     |     | ns   |

| t <sub>SU</sub>    | Data setup time, before SCLK rising edge | 8     |     | ns   |

| t <sub>DH</sub>    | Data hold time, after SCLK rising edge   | 8     |     | ns   |

| t <sub>DFS</sub>   | Data delay time from SCLK falling edge   |       | 15  | ns   |

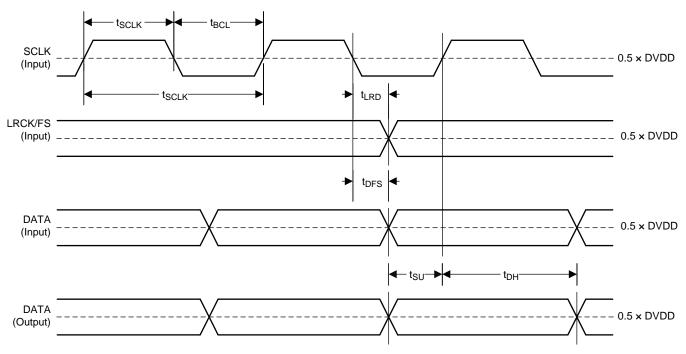

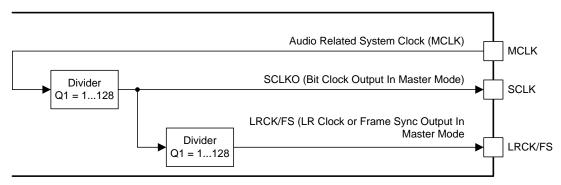

### 7.11 Serial Audio Port Timing – Master Mode

See Figure 3.

|                    | PARAMETER                                    | MIN | MAX | UNIT |

|--------------------|----------------------------------------------|-----|-----|------|

| t <sub>SCLK</sub>  | SCLK period                                  | 40  |     | ns   |

| t <sub>SCLKL</sub> | SCLK pulse width, low                        |     |     | ns   |

| t <sub>SCLKH</sub> | SCLK pulse width, high                       | 16  |     | ns   |

| t <sub>LRD</sub>   | LRCK/FS delay time from to SCLK falling edge | -10 | 20  | ns   |

| t <sub>SU</sub>    | Data setup time, before SCLK rising edge     | 8   |     | ns   |

| t <sub>DH</sub>    | Data hold time, after SCLK rising edge       | 8   |     | ns   |

| t <sub>DFS</sub>   | Data delay time from SCLK falling edge       |     | 15  | ns   |

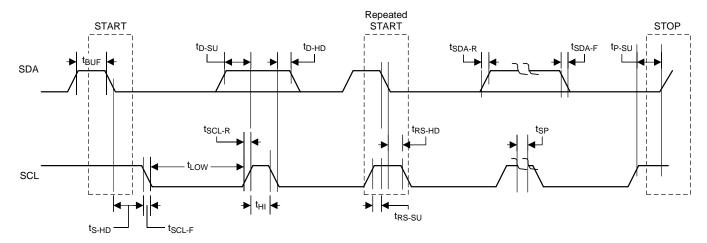

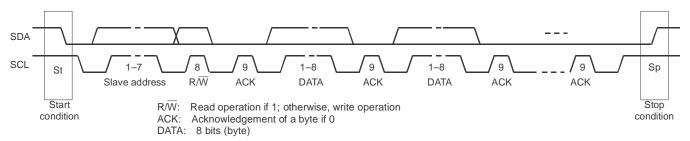

### 7.12 I<sup>2</sup>C Bus Timing –Standard

|                     |                                                                                       | MIN                    | MAX  | UNIT |

|---------------------|---------------------------------------------------------------------------------------|------------------------|------|------|

| f <sub>SCL</sub>    | SCL clock frequency                                                                   |                        | 400  | kHz  |

| t <sub>BUF</sub>    | Bus free time between a STOP and START condition                                      | 4.7                    |      | μs   |

| t <sub>LOW</sub>    | Low period of the SCL clock                                                           | 4.7                    |      | μs   |

| t <sub>HI</sub>     | High period of the SCL clock                                                          | 4                      |      | μs   |

| t <sub>RS-SU</sub>  | Setup time for (repeated) START condition                                             | 4.7                    |      | μs   |

| t <sub>S-HD</sub>   | Hold time for (repeated) START condition                                              | 4                      |      | μs   |

| t <sub>D-SU</sub>   | Data setup time                                                                       | 250                    |      | ns   |

| t <sub>D-HD</sub>   | Data hold time                                                                        | 0                      | 900  | ns   |

| t <sub>SCL-R</sub>  | Rise time of SCL signal                                                               | 20 + 0.1C <sub>B</sub> | 1000 | ns   |

| t <sub>SCL-R1</sub> | Rise time of SCL signal after a repeated START condition and after an acknowledge bit | 20 + 0.1C <sub>B</sub> | 1000 | ns   |

| t <sub>SCL-F</sub>  | Fall time of SCL signal                                                               | 20 + 0.1C <sub>B</sub> | 1000 | ns   |

| t <sub>SDA-R</sub>  | Rise time of SDA signal                                                               | 20 + 0.1C <sub>B</sub> | 1000 | ns   |

| t <sub>SDA-F</sub>  | Fall time of SDA signal                                                               | 20 + 0.1C <sub>B</sub> | 1000 | ns   |

| t <sub>P-SU</sub>   | Setup time for STOP condition                                                         | 4                      |      | μs   |

# 7.13 I<sup>2</sup>C Bus Timing –Fast

### See Figure 4.

|                     |                                                                                       | MIN                    | MAX | UNIT |

|---------------------|---------------------------------------------------------------------------------------|------------------------|-----|------|

| f <sub>SCL</sub>    | SCL clock frequency                                                                   |                        | 400 | kHz  |

| t <sub>BUF</sub>    | Bus free time between a STOP and START condition                                      | 1.3                    |     | μs   |

| $t_{LOW}$           | Low period of the SCL clock                                                           | 1.3                    |     | μs   |

| t <sub>HI</sub>     | High period of the SCL clock                                                          | 600                    |     | ns   |

| t <sub>RS-SU</sub>  | Setup time for (repeated)START condition                                              | 600                    |     | ns   |

| t <sub>RS-HD</sub>  | Hold time for (repeated)START condition                                               | 600                    |     | ns   |

| t <sub>D-SU</sub>   | Data setup time                                                                       | 100                    |     | ns   |

| t <sub>D-HD</sub>   | Data hold time                                                                        | 0                      | 900 | ns   |

| t <sub>SCL-R</sub>  | Rise time of SCL signal                                                               | 20 + 0.1C <sub>B</sub> | 300 | ns   |

| t <sub>SCL-R1</sub> | Rise time of SCL signal after a repeated START condition and after an acknowledge bit | 20 + 0.1C <sub>B</sub> | 300 | ns   |

| t <sub>SCL-F</sub>  | Fall time of SCL signal                                                               | 20 + 0.1C <sub>B</sub> | 300 | ns   |

| t <sub>SDA-R</sub>  | Rise time of SDA signal                                                               | 20 + 0.1C <sub>B</sub> | 300 | ns   |

| t <sub>SDA-F</sub>  | Fall time of SDA signal                                                               | 20 + 0.1C <sub>B</sub> | 300 | ns   |

| t <sub>P-SU</sub>   | Setup time for STOP condition                                                         | 600                    |     | ns   |

| t <sub>SP</sub>     | Pulse width of spike suppressed                                                       |                        | 50  | ns   |

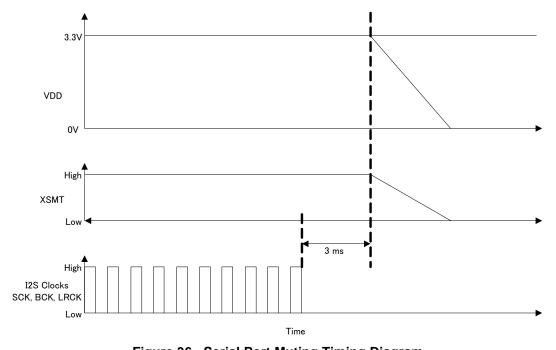

### 7.14 Timing Diagrams

This section contains timing diagrams for I<sup>2</sup>C and I<sup>2</sup>S / TDM.

Figure 1. Timing Requirements for MCLK Input

Figure 2. MCLK Timing Diagram in Slave Mode

Copyright © 2018, Texas Instruments Incorporated

Product Folder Links: *TAS3251*

### **Timing Diagrams (continued)**

Figure 3. MCLK Timing Diagram in Master Mode

Figure 4. I<sup>2</sup>C Communication Port Timing Diagram

16 Subm

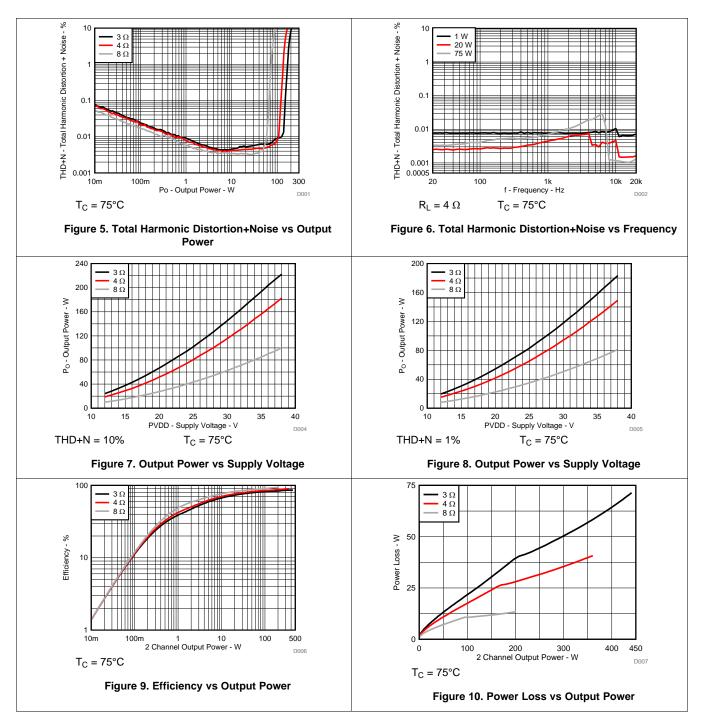

### 7.15 Typical Characteristics

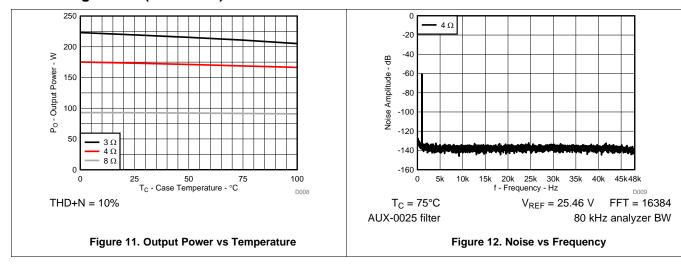

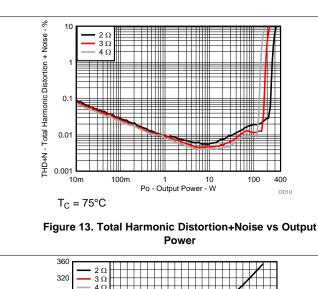

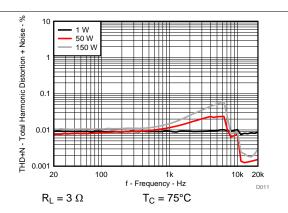

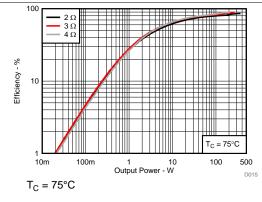

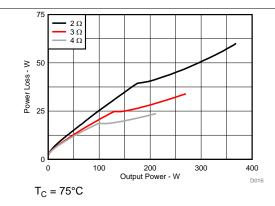

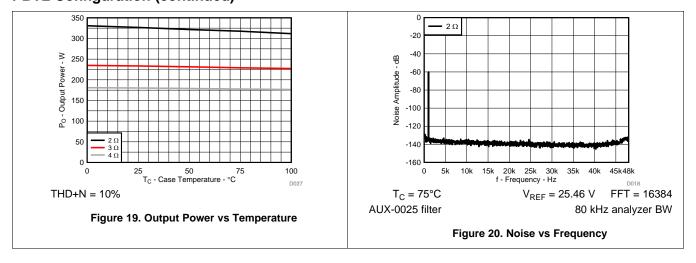

### 7.15.1 BTL Configuration

All Measurements taken at audio frequency = 1 kHz, PVDD\_X = 36 V, GVDD\_X = 12 V,  $R_L$  = 4  $\Omega$ ,  $f_S$  = 600 kHz,  $R_{OC}$  = 22 k $\Omega$ ,  $T_C$  = 75°C, Output Filter:  $L_{DEM}$  = 10  $\mu$ H,  $C_{DEM}$  = 1  $\mu$ F, MODE = 0, AES17 + AUX-0025 measurement filters, unless otherwise noted.

Submit Documentation Feedback

### **BTL Configuration (continued)**

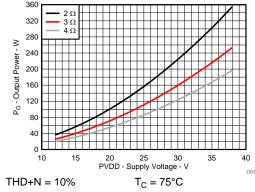

### 7.15.2 PBTL Configuration

All Measurements taken at audio frequency = 1 kHz, PVDD\_X = 36 V, GVDD\_X = 12 V,  $R_L = 2 \Omega$ ,  $f_S = 600$  kHz,  $R_{OC}$  = 22 k $\Omega$ ,  $T_{C}$  = 75 °C, Output Filter:  $L_{DEM}$  = 10  $\mu$ H,  $C_{DEM}$  = 1  $\mu$ F, MODE = 1, outputs paralleled after LC filter, AES17 + AUX-0025 measurement filters, unless otherwise noted.

Figure 14. Total Harmonic Distortion+Noise vs Frequency

Figure 15. Output Power vs Supply Voltage

Figure 16. Output Power vs Supply Voltage

Figure 17. Efficiency vs Output Power

Figure 18. Power Loss vs Output Power

Submit Documentation Feedback

### **PBTL Configuration (continued)**

### **Detailed Description**

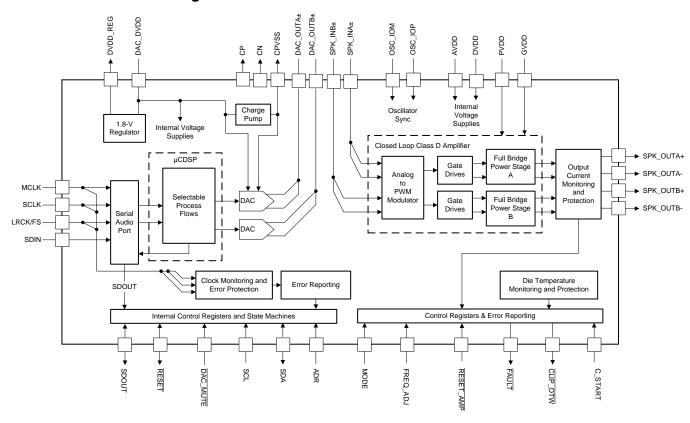

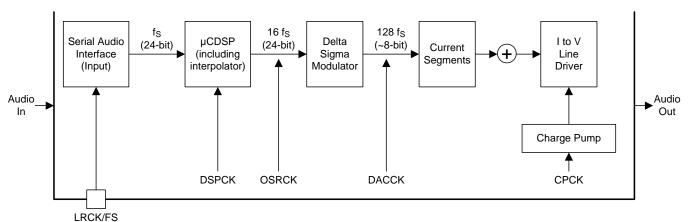

### Overview 8.1

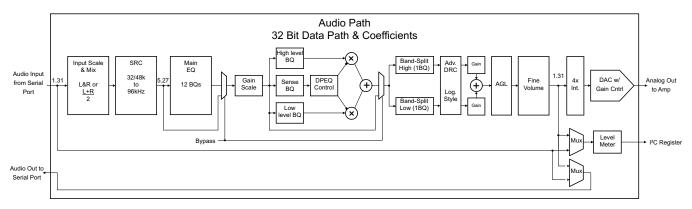

The TAS3251 device integrates four main building blocks into a single cohesive device that maximizes sound quality, flexibility, and ease of use. These include:

- Burr-Brown™ stereo audio DAC with a highly flexible serial audio port

- μCDSP, TI's latest audio processing core with a pre-programmed DSP audio process flows

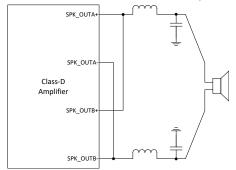

- High-Performance, Ultra-HD Closed-loop Class-D amplifier capable of operating in stereo or mono

- An I<sup>2</sup>C control port for communication and control of the device

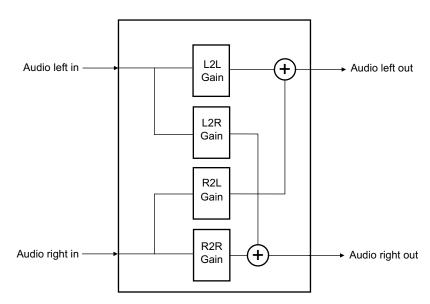

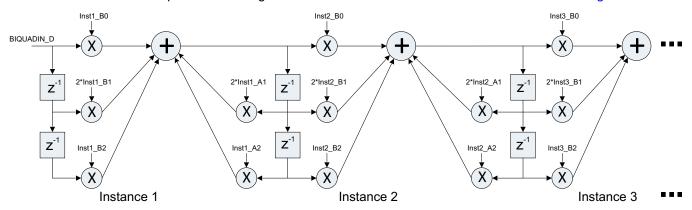

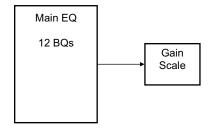

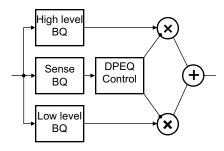

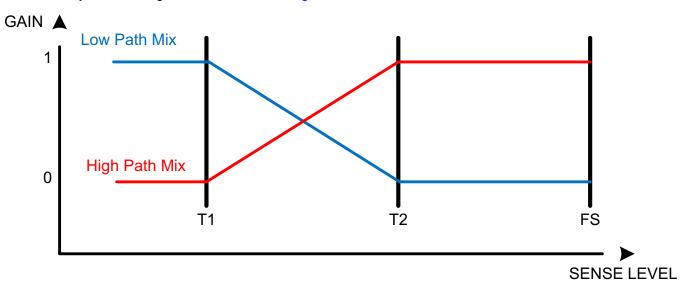

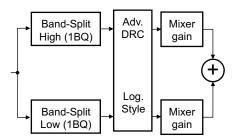

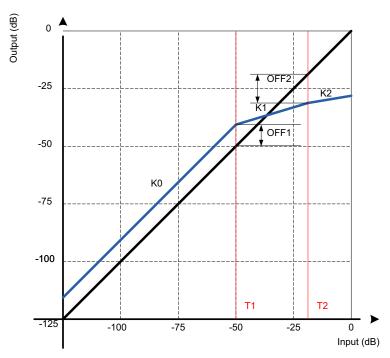

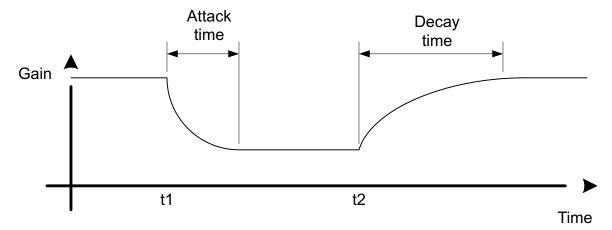

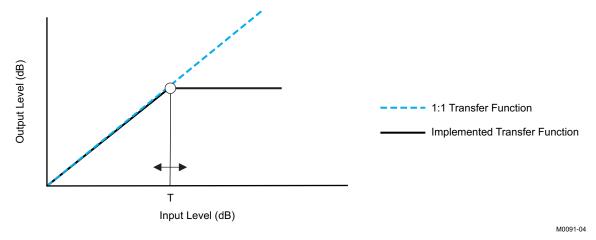

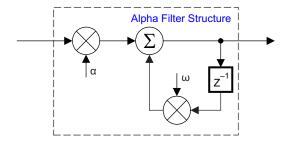

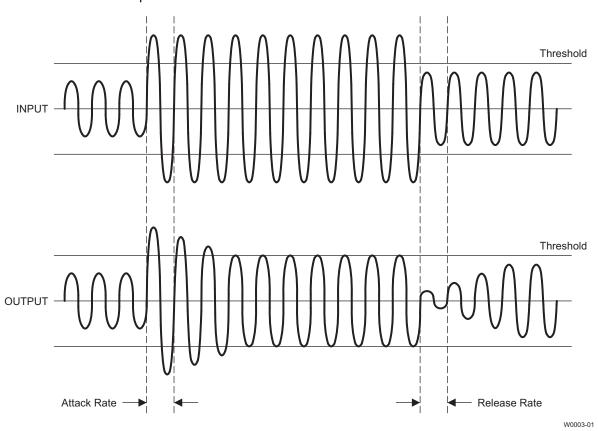

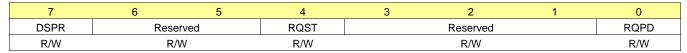

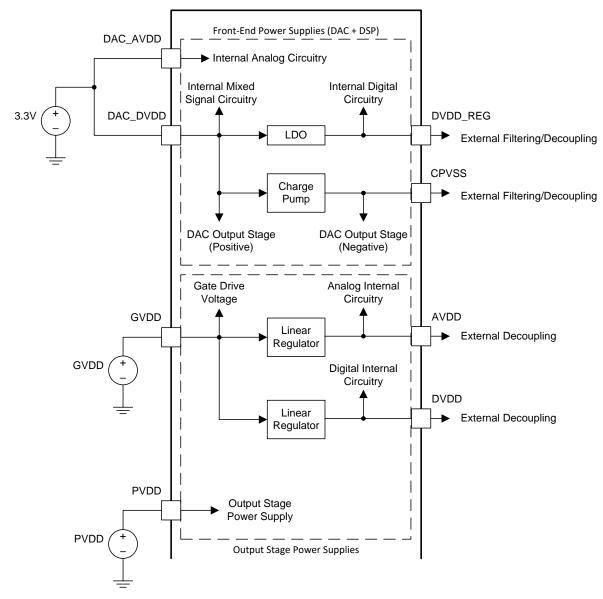

The device requires three power supplies for proper operation. A 3.3 V rail for the low voltage circuitry and DAC, a 12 V rail for the amplifier gate-drive, and PVDD which is required to provide power to the output stage of the audio amplifier. The operating range for these supplies is shown in the *Recommended Operating Conditions*.