# SCANSTA101 Low Voltage IEEE 1149.1 System Test Access (STA) Master

Check for Samples: SCANSTA101

### **FEATURES**

- Compatible with IEEE Std. 1149.1 (JTAG) Test Access Port and Boundary Scan Architecture

- Supported by Texas Instruments' SCAN Ease (SCAN Embedded Application Software Enabler) Software Rev 2.0

- Uses Generic, Asynchronous Processor Interface; Compatible with a Wide Range of Processors and Processor Clock (PCLK) Frequencies

- 16-Bit Data Interface (IP Scalable to 32-bit)

- 2k x 32 Bit Dual-Port Memory

- Load-on-the-Fly (LotF) and Preloaded Vector Operating Modes Supported

- On-Board Sequencer Allows Multi-Vector Operations such as those Required to Load Data Into an FPGA

- On-Board Compares Support Test Data In (TDI) Validation Against Preloaded Expected Data

- 32-Bit Linear Feedback Shift Register (LFSR) at the Test Data In (TDI) Port for Signature Compression

- State, Shift, and BIST Macros Allow Predetermined Test Mode Select (TMS) Sequences to be Utilized

- Operates at 3.3 V Supply Voltages with 5 V Tolerant I/O

- Outputs Support Power-Down TRI-STATE Mode.

### DESCRIPTION

The SCANSTA101 is designed to function as a test master for an IEEE 1149.1 boundary scan test system. It is suitable for use in embedded IEEE 1149.1 applications and as a component in a standalone boundary scan tester.

The SCANSTA101 is an enhanced version of, and a replacement for, the SCANPSC100. The SCANSTA101 supports the IEEE 1149.1 Test Access Port (TAP) standard and the IEEE 1532 standard for in-system configuration of programmable devices.

The SCANSTA101 improves test vector throughput and reduces software overhead in the system processor. The SCANSTA101 presents a simple, register-based interface to the system processor. Texas Instruments provides C-language source code which can be included in the embedded system software. The combination of the SCANSTA101 and its support software comprises a simple API for boundary scan operations.

The interface from the SCANSTA101 to the system processor is implemented by reading and writing registers, some of which map to locations in the SCANSTA101 memory. Hardware handshaking and interrupt lines are provided as part of the processor interface.

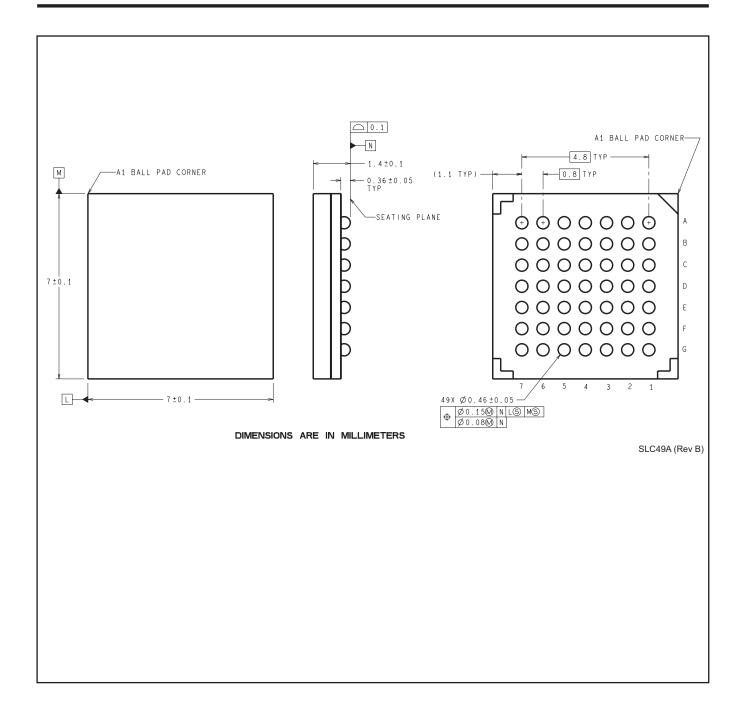

The SCANSTA101 is available as a stand-alone device packaged in a 49-pin NFBGA package. It is also available as an IP macro for synthesis in programmable logic devices.

M

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

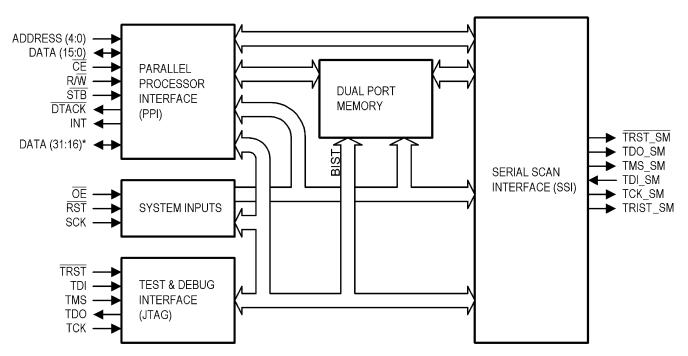

#### SCANSTA101 ARCHITECTURE

<sup>\*</sup> Note: IP data bus width can be configured for 16 or 32 bit applications. Silicon data bus width is fixed at 16 bits.

Figure 1. SCANSTA101 STA Master and Interfaces

Figure 1 shows a high level view of the SCANSTA101 STA Master and its interfaces. Table 1 provides a brief description of each of these interfaces. provides a brief description of the device pins and their functions. The device is composed of three interfaces around a dual-port memory. These interfaces are the Parallel Processor Interface (PPI), Serial Scan Interface (SSI), and Test and Debug Interface. The System Input block designates inputs that have global use across the device.

The Test and Debug Interface supports BIST, boundary scan, and internal scan for the SCANSTA101.

**Table 1. INTERFACE DESCRIPTIONS**

| Interface                    | Description                                                                                                                     |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| Parallel Processor Interface | Used for configuration, ScanMaster scan chain loads and reads, programmable device file loads and reads, and status monitoring. |

| Serial Scan Interface        | Performs parallel to serial conversion, sequences and formats the outgoing serial stream to conform to 1149.1 protocol.         |

| Test and Debug Interface     | IEEE 1149.1 TAP                                                                                                                 |

| System Inputs                | Interface inputs for system control, i.e. clock, reset and output tristate control.                                             |

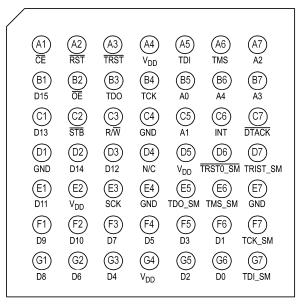

### **CONNECTION DIAGRAM**

Figure 2. NFBGA Package Pinout (Top View)

### **PIN DESCRIPTIONS**

| Pin<br>Name             | No. Pins | 1/0 | Description                                                                                                                                                                                                                                                                                                              |

|-------------------------|----------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| vcc                     | 4        | N/A | Power                                                                                                                                                                                                                                                                                                                    |

| GND                     | 4        | N/A | Ground                                                                                                                                                                                                                                                                                                                   |

| D(15:0)                 | 16       | I/O | Bidirectional Data Bus. Signals are bonded out for the packaged device.                                                                                                                                                                                                                                                  |

| D(31:16) <sup>(1)</sup> | 16       | I/O | Bidirectional Data Bus. These signals are not available in the packaged device.                                                                                                                                                                                                                                          |

| A(4:0)                  | 5        | I   | Address Bus                                                                                                                                                                                                                                                                                                              |

| SCK                     | 1        | I   | The system clock that drives all internal timing. TCK_SM is a gated, divided and buffered version of SCK.                                                                                                                                                                                                                |

| INT                     | 1        | 0   | Interrupt Output                                                                                                                                                                                                                                                                                                         |

| ŌĒ                      | 1        | I   | Output enable that will TRI-STATE all 1149.1 "_SM" outputs when high.                                                                                                                                                                                                                                                    |

| DTACK                   | 1        | 0   | DTACK is used to synchronize asynchronous transfers between the host and the SCANSTA101. When CE is high, DTACK is tristated. When CE is low, DTACK is enabled. DTACK goes low when data has been registered and then goes tri-state when the cycle has completed.                                                       |

| R/W                     | 1        | I   | $R/\overline{W}$ defines a PPI cycle. Read when high, write when low.                                                                                                                                                                                                                                                    |

| STB                     | 1        | ı   | Strobe is used for timing all PPI transfers. D(15:0), or D(31:0) in 32-bit mode $^{(1)}$ , are at TRI-STATE when $\overline{\text{STB}}$ is high. Data valid setup is with respect to the <u>falling</u> edge of $\overline{\text{STB}}$ and data valid hold is with respect to rising edge of $\overline{\text{STB}}$ . |

| CE                      | 1        | I   | Chip Enable, when low, enables the PPI for data transfers. $\overline{\text{CE}}$ can remain low during back-to-back accesses. D(15:0), or D(31:0) in 32-bit mode <sup>(1)</sup> , and $\overline{\text{DTACK}}$ are tristated when $\overline{\text{CE}}$ is high.                                                      |

| RST                     | 1        | I   | Asynchronous reset, when low, initializes the SCANSTA101.                                                                                                                                                                                                                                                                |

| TDO                     | 1        | 0   | Test Data Out is the serial scan output from the SCANSTA101. TDO is enabled when $\overline{\text{OE}}$ is low.                                                                                                                                                                                                          |

<sup>(1)</sup> D(31:16) in the Parallel Processor Interface and TRST1\_SM in the Serial Scan Interface are not bonded out for the packaged device. These are used in the 32-bit IP Macro Mode only.

## **PIN DESCRIPTIONS (continued)**

| Pin<br>Name  | No. Pins | I/O | Description                                                                                                                                                                                                        |

|--------------|----------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TDI          | 1        | I   | Test Data In is the serial scan input to the SCANSTA101.                                                                                                                                                           |

| TMS          | 1        | 1   | Test Mode Select. The Test Mode Select pin is a serial input used to accept control logic to the test & debug interface.                                                                                           |

| TCK          | 1        | 1   | Test Clock Input for 1149.1                                                                                                                                                                                        |

| TRST         | 1        | I   | Test Reset. This pin should be tied to ground by a 1K resistor to hold the Test and Debug Interface in the Test-Logic-Reset state during device power-up. This avoids invalid states when ramping supply voltages. |

| TDI_SM       | 1        | I   | STA Master Test Data Input in the Serial Scan Interface                                                                                                                                                            |

| TDO_SM       | 1        | 0   | STA Master Test Data Output in the Serial Scan Interface                                                                                                                                                           |

| TMS_SM       | 1        | 0   | STA Master Test Mode Select in the Serial Scan Interface                                                                                                                                                           |

| TCK_SM       | 1        | 0   | STA Master Test Clock in the Serial Scan Interface                                                                                                                                                                 |

| TRST0_SM     | 1        | 0   | STA Master Test Reset output in the Serial Scan Interface                                                                                                                                                          |

| TRST1_SM (1) | 1        | 0   | Redundant ScanMaster TRST. This signal is not available for the packaged device.                                                                                                                                   |

| TRIST_SM     | 1        | 0   | The TRI-STATE notification pin exerts a high signal when TDO_SM is at TRI-STATE                                                                                                                                    |

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

www.ti.com

## **ABSOLUTE MAXIMUM RATINGS (1)(2)**

| Supply Voltage (V <sub>CC</sub> )                   |                        | -0.5V to +4.0V |

|-----------------------------------------------------|------------------------|----------------|

| DC Input Diode Current (I <sub>IK</sub> )           | V <sub>I</sub> = −0.5V | −20 mA         |

| DC Input Voltage (V <sub>I</sub> ) -0.5V to +4.0V   |                        |                |

| DC Output Diode Current (I <sub>OK</sub> )          | V <sub>O</sub> = −0.5V | −20 mA         |

| DC Output Voltage (V <sub>O</sub> ) -0.5V to +4.0V  |                        |                |

| DC Output Source/Sink Current (I <sub>O</sub> )     |                        | ±50 mA         |

| DC V <sub>CC</sub> or Ground Current per Output Pin |                        | ±50 mA         |

| DC Latchup Source or Sink Current                   |                        | ±300 mA        |

| Junction Temperature                                | Plastic                | +150°C         |

| Storage Temperature −65°C to +150°C                 |                        |                |

| Lead Temperature (Solder, 4sec)                     | 49L NFBGA              | 220°C          |

| Max Pkg Power Capacity @ 25°C                       | 49L NFBGA              | 1.47W          |

| Thermal Resistance (θ <sub>JA</sub> )               | 49L NFBGA              | 85°C/W         |

| Package Derating 11.8mW/°C above +25°C              |                        |                |

| ESD Last Passing Voltage (Min)                      |                        | 2000V          |

<sup>(1)</sup> Absolute maximum ratings are those values beyond which damage to the device may occur. The datasheet specifications should be met, without exception, to ensure that the system design is reliable over its power supply, temperature, and output/input loading variables. Texas Instruments does not recommend operation of SCAN STA products outside of recommended operation conditions.

### RECOMMENDED OPERATING CONDITIONS

| Supply Voltage (V <sub>CC</sub> )       | 3.0V to 3.6V          |

|-----------------------------------------|-----------------------|

| Input Voltage (V <sub>I</sub> )         | 0V to V <sub>CC</sub> |

| Output Voltage (V <sub>O</sub> )        | 0V to V <sub>CC</sub> |

| Operating Temperature (T <sub>A</sub> ) | −40°C to +85°C        |

### DC ELECTRICAL CHARACTERISTICS

Over recommended operating supply voltage and temperature ranges unless otherwise specified.

| Symbol           | Parameter                                                                  | Conditions                                                                                                                  | Min                   | Max  | Units |

|------------------|----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-----------------------|------|-------|

| V <sub>IH</sub>  | Minimum High Input Voltage                                                 | $V_{OUT} = 0.1V$ or $V_{CC} - 0.1V$                                                                                         | 2.1                   |      | V     |

| V <sub>IL</sub>  | Maximum Low Input Voltage                                                  | $V_{OUT} = 0.1V$ or $V_{CC} - 0.1V$                                                                                         |                       | 0.8  | V     |

| V <sub>OH</sub>  | Minimum High Output Voltage                                                | $I_{OUT} = -100 \mu A$ , $V_{IN} = V_{IL} \text{ or } V_{IH}$                                                               | V <sub>CC</sub> -0.2V |      | V     |

|                  | Minimum High Output Voltage, TDO_SM, TMS_SM, TCK_SM, TRST0_SM outputs only | $I_{OH} = -24 \text{ mA}, V_{IN} = V_{IL} \text{ or } V_{IH}$                                                               | 2.2                   |      | V     |

|                  | Minimum High Output Voltage,<br>All other outputs including 1149.1         | $I_{OH} = -12 \text{ mA}, V_{IN} = V_{IL} \text{ or } V_{IH}$                                                               | 2.4                   |      | V     |

| $V_{OL}$         | Maximum Low Output Voltage                                                 | $I_{OUT}$ = +100 $\mu$ A, $V_{IN}$ = $V_{IL}$ or $V_{IH}$                                                                   |                       | 0.2  | V     |

| 02               | Maximum Low Output Voltage, TDO_SM, TMS_SM, TCK_SM, TRST0_SM outputs only  | $I_{OL}$ = 24 mA, $V_{IN}$ = $V_{IL}$ or $V_{IH}$                                                                           |                       | 0.5  | V     |

|                  | Maximum Low Output Voltage, all other outputs including 1149.1             | $I_{OL} = 12mA$ , $V_{IN} = V_{IL}$ or $V_{IH}$                                                                             |                       | 0.4  | V     |

| I <sub>IN</sub>  | Maximum Input Leakage Current, All pins except TDI, TMS, TRST, TDI_SM      | $V_{IN} = V_{CC}$ for TDI, $\overline{OE}$ , $V_{IN} = V_{CC}$ , GND for All Others                                         |                       | ±5.0 | μА    |

| I <sub>ILR</sub> | Maximum Input Leakage Current, TDI, TMS, TRST, TDI_SM                      | V <sub>IN</sub> = GND                                                                                                       | -45                   | -200 | μA    |

| I <sub>IH</sub>  | Maximum Input Leakage Current, TDI, TMS, TRST, TDI_SM                      | V <sub>IN</sub> = V <sub>CC</sub>                                                                                           |                       | 5.0  | μА    |

| l <sub>OZ</sub>  | Maximum TRI-STATE Leakage Current                                          | $V_{IN}$ = V <sub>CC</sub> , GND, V <sub>IN</sub> ( $\overline{OE}$ , R/ $\overline{W}$ , $\overline{CE}$ , STB) = VIL, VIH |                       | ±5.0 | μА    |

<sup>(2)</sup> If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/ Distributors for availability and specifications.

### DC ELECTRICAL CHARACTERISTICS (continued)

Over recommended operating supply voltage and temperature ranges unless otherwise specified.

| Symbol             | Parameter                                                            | Conditions               | Min | Max | Units |

|--------------------|----------------------------------------------------------------------|--------------------------|-----|-----|-------|

| I <sub>OFF</sub>   | Power Off Leakage Current All pins except TDI, TMS, TRST, and TDI_SM | V <sub>CC</sub> = 0.0V   |     | 5.0 | μΑ    |

| I <sub>CC</sub>    | Maximum Quiescent Supply Current                                     |                          |     | 250 | μΑ    |

| I <sub>CCmax</sub> | Maximum Supply Current                                               | All inputs low           |     | 1.2 | mA    |

| I <sub>CCT</sub>   | Maximum I <sub>CC</sub> /Input                                       | $V_{IN} = V_{CC} - 0.6V$ |     | 250 | μΑ    |

#### AC ELECTRICAL CHARACTERISTICS/OPERATING REQUIREMENTS

Over recommended operating supply voltage and temperature ranges unless otherwise specified.  $C_L = 50 \text{ pF}$ ,  $R_L = 500\Omega$  unless otherwise specified.

| Symbol          | Parameter                                                                        | Conditions                  | # of SCK<br>(1)(2) | Min | Max  | Units |

|-----------------|----------------------------------------------------------------------------------|-----------------------------|--------------------|-----|------|-------|

| PARALLEL        | PROCESSOR INTERFACE (PPI)                                                        | +                           |                    | +   | 1    | 1     |

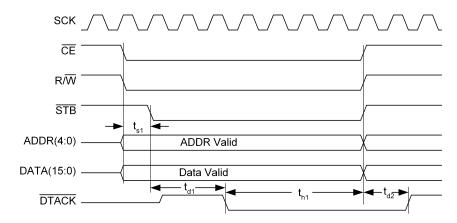

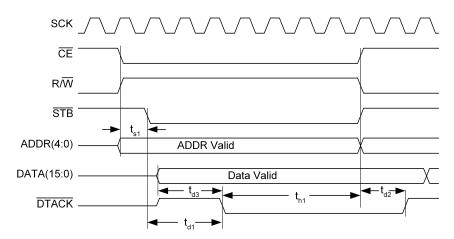

| t <sub>S1</sub> | Set Up Time CE, R/W, Addr, Data to STB                                           | See Figure 12 and Figure 13 |                    | 0   |      | ns    |

| t <sub>H1</sub> | Hold Time CE, R/W, Addr, Data to DTACK                                           | See Figure 12 and Figure 13 |                    | 0   |      | ns    |

| t <sub>D1</sub> | Propagation Delay STB low to DTACK low, Register Write                           | See Figure 12               | 2 or 3             |     | 11.5 | ns    |

| t <sub>D1</sub> | Propagation Delay STB low to DTACK low, Register Read                            | See Figure 13               | 4 or 5             |     | 11.5 | ns    |

| t <sub>D1</sub> | Propagation Delay STB low to DTACK low, Memory Write: 16-bit first access        | See Figure 12               | 3 or 4             |     | 11.5 | ns    |

| t <sub>D1</sub> | Propagation Delay STB low to DTACK low, Memory Write: 16-bit second access       | See Figure 12               | 7 or 8             |     | 11.5 | ns    |

| t <sub>D1</sub> | Propagation Delay STB low to DTACK low, Memory Read: 16-bit first access         | See Figure 13               | 9 or 10            |     | 11.5 | ns    |

| t <sub>D1</sub> | Propagation Delay STB low to DTACK low, Memory Read: 16-bit second access        | See Figure 13               | 3 or 4             |     | 11.5 | ns    |

| t <sub>D2</sub> | Propagation Delay STB high to DTACK TRISTATE, Register Write                     | See Figure 12               | 1 or 2             |     | 10.0 | ns    |

| t <sub>D2</sub> | Propagation Delay STB high to DTACK TRISTATE, Register Read                      | See Figure 13               | 1 or 2             |     | 10.0 | ns    |

| t <sub>D2</sub> | Propagation Delay STB high to DTACK TRISTATE, Memory Write: 16-bit first access  | See Figure 12               | 1 or 2             |     | 10.0 | ns    |

| t <sub>D2</sub> | Propagation Delay STB high to DTACK TRISTATE, Memory Write: 16-bit second access | See Figure 12               | 1 or 2             |     | 10.0 | ns    |

| t <sub>D2</sub> | Propagation Delay STB high to DTACK TRISTATE, Memory Read: 16-bit first access   | See Figure 13               | 1 or 2             |     | 10.0 | ns    |

| t <sub>D2</sub> | Propagation Delay STB high to DTACK TRISTATE, Memory Read: 16-bit second access  | See Figure 13               | 1 or 2             |     | 10.0 | ns    |

<sup>(1)</sup> Due to uncertainty in the relationship of the STB placement to the system clock, SCK, the STB may be detected during the current or the next SCK cycle.

<sup>(2)</sup> An absolute maximum delay can be calculated as: (Max # SCK) x (SCK Period) + t<sub>D</sub>.For example, for t<sub>D1</sub> (STB low to DTACK low, register write), the # SCK cycles is 2 or 3 and the delay, t<sub>D</sub>, is 11.5ns. For a SCK with a 100ns period, the absolute maximum delay is (3 x 100ns) + 11.5, or 311.5ns.

# AC ELECTRICAL CHARACTERISTICS/OPERATING REQUIREMENTS (continued)

Over recommended operating supply voltage and temperature ranges unless otherwise specified.  $C_L = 50 \text{ pF}$ ,  $R_L = 500\Omega$  unless otherwise specified.

| Symbol               | Parameter                                                                     | Conditions    | # of SCK<br>(1)(2) | Min | Max  | Units |

|----------------------|-------------------------------------------------------------------------------|---------------|--------------------|-----|------|-------|

| t <sub>D3</sub>      | Propagation Delay Output data valid to DTACK low, all read cycles             | See Figure 13 | 1                  |     |      | ns    |

| t <sub>pHL1</sub>    | Propagation Delay<br>STB low to INT low, register write (clears<br>Interrupt) | See Figure 12 | 5 or 6             |     | 10.5 | ns    |

| $t_{W}$              | Clock Pulse Width, SCK, H or L                                                |               |                    | 3.0 |      | ns    |

| f <sub>MAX</sub>     | Clock Frequency, SCK                                                          |               |                    |     | 66   | MHz   |

| t <sub>RELEASE</sub> | Release Time, RST to STB                                                      |               | 2                  |     |      | ns    |

| Symbol            | Parameter                                                    | Conditions    | Min  | Max  | Units |

|-------------------|--------------------------------------------------------------|---------------|------|------|-------|

| SERIAL SO         | CAN INTERFACE (SSI)                                          |               |      |      |       |

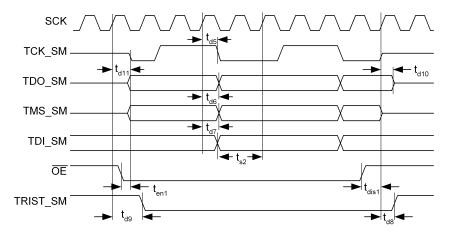

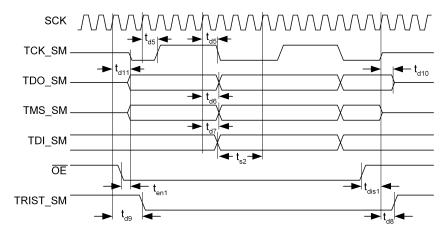

| t <sub>D5</sub>   | Propagation Delay<br>SCK to TCK_SM                           | See Figure 14 |      | 11.5 | ns    |

| $t_{D6}$          | Propagation Delay<br>SCK to TDO_SM                           | See Figure 14 |      | 12.0 | ns    |

| t <sub>D7</sub>   | Propagation Delay<br>SCK to TMS_SM                           | See Figure 14 |      | 12.5 | ns    |

| t <sub>D8</sub>   | Propagation Delay - tpLH<br>SCK to TRIST_SM                  | See Figure 14 |      | 15.0 | ns    |

| t <sub>D9</sub>   | Propagation Delay - tpHL<br>SCK to TRIST_SM                  | See Figure 14 |      | 12.5 | ns    |

| t <sub>D10</sub>  | Propagation Delay<br>SCK to TDO_SM disable                   | See Figure 14 |      | 12.5 | ns    |

| t <sub>D11</sub>  | Propagation Delay<br>SCK to TDO_SM enable                    | See Figure 14 |      | 14.0 | ns    |

| t <sub>EN1</sub>  | Enable Delay OE low to TCK_SM, TDO_SM, TMS_SM, or TRST0_SM   | See Figure 14 |      | 12.0 | ns    |

| t <sub>DIS1</sub> | Disable Delay OE high to TCK_SM, TDO_SM, TMS_SM, or TRST0_SM | See Figure 14 |      | 11.0 | ns    |

| t <sub>EN2</sub>  | Enable Delay OE low to TRIST_SM                              |               |      | 10.0 | ns    |

| t <sub>DIS2</sub> | Disable Delay OE high to TRIST_SM                            |               |      | 11.5 | ns    |

| t <sub>DIS3</sub> | Disable Delay RST low to TRST0_SM                            |               |      | 12.5 | ns    |

| t <sub>S2</sub>   | Setup Time<br>SCK to TDI_SM                                  | See Figure 14 | 3.5  |      | ns    |

| t <sub>H2</sub>   | Hold Time<br>SCK to TDI_SM                                   | See Figure 14 | 2.0  |      | ns    |

| TEST & DE         | BUG INTERFACE TIMING REQUIREMENTS (                          | SCAN)         | ,    |      |       |

| t <sub>S</sub>    | Setup Time<br>TMS to TCK                                     |               | 2.0  |      | ns    |

| t <sub>H</sub>    | Hold Time<br>TMS to TCK                                      |               | 1.0  |      | ns    |

| ts                | Setup Time<br>TDI to TCK                                     |               | 1.0  |      | ns    |

| t <sub>H</sub>    | Hold Time<br>TDI to TCK                                      |               | 2.0  |      | ns    |

| t <sub>W</sub>    | Pulse Width<br>TCK (H or L)                                  |               | 10.0 |      | ns    |

| Symbol           | Parameter                      | Conditions | Min | Max | Units |

|------------------|--------------------------------|------------|-----|-----|-------|

| t <sub>WL</sub>  | Reset Pulse Width TRST (L)     |            | 2.5 |     | ns    |

| t <sub>REC</sub> | Recovery Time<br>TCK from TRST |            | 2.0 |     | ns    |

| f <sub>MAX</sub> | Maximum Clock Frequency, TCK   |            |     | 25  | MHz   |

### APPLICATIONS/PROGRAMMERS REFERENCE

### **Table 2. REGISTER SUMMARY**

| Address | Туре | Mnemonic | Register                      | Active Register Bits | Reset Value |

|---------|------|----------|-------------------------------|----------------------|-------------|

| 00h     | RW   | START    | Start Register                | 5                    | 0000h       |

| 01h     | RW   | STATUS   | Status Register               | 10                   | 0000h       |

| 02h     | RW   | INTCTRL  | Interrupt Control Register    | 8                    | 0000h       |

| 03h     | RW   | INTSTAT  | Interrupt Status Register     | 8                    | 0000h       |

| 04h     | RW   | SETUPR   | Setup Register                | 8                    | 0043h       |

| 05h     | RW   | CLKDIV   | Clock Divider Register        | 6                    | 0000h       |

| 07h     | RW   | EXPR     | TDI_SM LFSR Exponent Register | 3                    | 0000h       |

| 08h     | RW   | LSSEDR   | TDI_SM LSB Seed Register      | 16                   | 0000h       |

| 09h     | RW   | MSSEDR   | TDI_SM MSB Seed Register      | 16                   | 0000h       |

| 0Ah     | RW   | LSRESR   | TDI_SM LSB Result Register    | 16                   | 0000h       |

| 0Bh     | RW   | MSRESR   | TDI_SM MSB Result Register    | 16                   | 0000h       |

| 0Ch     | RW   | INDEXR   | Index Register                | 16                   | 0000h       |

| 11h     | RW   | VINDEXR  | Vector Index Register         | 16                   | 0000h       |

| 13h     | RW   | HTINDEXR | Header/Trailer Index Register | 16                   | 0000h       |

| 15h     | RW   | MINDEXR  | Macro Index Register          | 16                   | 0000h       |

| 17h     | RW   | SINDEXR  | Sequencer Index Register      | 16                   | 0000h       |

| 19h     | RW   | BSINDEXR | Bridge Support Register       | 16                   | 0000h       |

### Table 3. MEMORY/REGISTER ADDRESS MAP

| A4 | А3 | A2 | A1 | A0 | Function                         | Base Address | Long Word Index     | Structure/Size  |

|----|----|----|----|----|----------------------------------|--------------|---------------------|-----------------|

| 0  | 0  | 0  | 0  | 0  | Start                            | N/A          | N/A                 | 16-bit Register |

| 0  | 0  | 0  | 0  | 1  | Status                           | N/A          | N/A                 | 16-bit Register |

| 0  | 0  | 0  | 1  | 0  | Interrupt Control                | N/A          | N/A                 | 16-bit Register |

| 0  | 0  | 0  | 1  | 1  | Interrupt Status                 | N/A          | N/A                 | 16-bit Register |

| 0  | 0  | 1  | 0  | 0  | Setup                            | N/A          | N/A                 | 16-bit Register |

| 0  | 0  | 1  | 0  | 1  | 1 Clock Divider N/A N/A          |              | N/A                 | 16-bit Register |

| 0  | 0  | 1  | 1  | 1  | 1 TDI_SM LFSR Exponent N/A N/A   |              | 16-bit Register     |                 |

| 0  | 1  | 0  | 0  | 0  | D TDI_SM LFSR LSB Seed N/A N/A 1 |              | 16-bit Register (1) |                 |

| 0  | 1  | 0  | 0  | 1  | TDI_SM LFSR MSB Seed N/A N/A 1   |              | 16-bit Register (1) |                 |

| 0  | 1  | 0  | 1  | 0  |                                  |              | 16-bit Register (1) |                 |

| 0  | 1  | 0  | 1  | 1  |                                  |              | 16-bit Register (1) |                 |

| 0  | 1  | 1  | 0  | 0  |                                  |              | 16-bit Register (2) |                 |

| 0  | 1  | 1  | 0  | 1  | TDO_SM 0 0 - 0x1BF See (3)       |              | See (3)             |                 |

| 0  | 1  | 1  | 1  | 0  | TDI_SM                           |              | See (3)             |                 |

<sup>(1)</sup> The TDI\_SM LFSR result and seed registers require two sequential reads/writes for each register pair.

3) The actual address is calculated from the base address of the memory area plus the content of its address pointer.

<sup>(2)</sup> The Index register is used to set the individual address pointers. Writing to the Index register will set each of the individual address pointers (TDO\_SM, TDI\_SM, Expected, and Mask). The individual address pointers will automatically increment with each long word read from TDI\_SM or each long word written to the TDO\_SM, Expected, or Mask memory spaces.

### Table 3. MEMORY/REGISTER ADDRESS MAP (continued)

| A4 | А3 | A2 | A1 | Α0 | Function                  | Base Address | Long Word Index | Structure/Size               |

|----|----|----|----|----|---------------------------|--------------|-----------------|------------------------------|

| 0  | 1  | 1  | 1  | 1  | Expected                  | 0 x 380      | 0 - 0x1BF       | See (3)                      |

| 1  | 0  | 0  | 0  | 0  | Mask                      | 0 x 540      | 0 - 0x1BF       | See (3)                      |

| 1  | 0  | 0  | 0  | 1  | Vector Index              | N/A          | N/A             | 16-bit Register              |

| 1  | 0  | 0  | 1  | 0  | Vector 1                  | 0 x 700      | 0x0 - 0x1       | See <sup>(4)</sup> , Table 4 |

|    |    |    |    |    | Vector 2                  | 0 x 700      | 0x2 - 0x3       |                              |

|    |    |    |    |    | Vector 3                  | 0 x 700      | 0x4 - 0x5       |                              |

|    |    |    |    |    | Vector 4                  | 0 x 700      | 0x6 - 0x7       |                              |

| 1  | 0  | 0  | 1  | 1  | Header/Trailer Index      | N/A          | N/A             | 16-bit Register              |

| 1  | 0  | 1  | 0  | 0  | Data Header               | 0 x 708      | 0x0 - 0x1F      | See Table 5                  |

|    |    |    |    |    | Data Trailer              | 0 x 728      | 0x20 - 0x3F     |                              |

|    |    |    |    |    | Instruction Header        | 0 x 748      | 0x40 - 0x5F     |                              |

|    |    |    |    |    | Instruction Trailer       | 0 x 768      | 0x60 - 0x7F     |                              |

| 1  | 0  | 1  | 0  | 1  | Macro Index               | N/A          | N/A             | 16-bit Register              |

| 1  | 0  | 1  | 1  | 0  | Macro 1                   | 0 x 788      | 0x0             | See Table 6,                 |

|    |    |    |    |    | Macro 2                   | 0 x 789      | 0x1             | Table 7 and Table 8          |

|    |    |    |    |    | Macro 3                   | 0 x 78A      | 0x2             | Table 0                      |

|    |    |    |    |    | Macro 16                  | 0 x 797      | 0xF             |                              |

| 1  | 0  | 1  | 1  | 1  | Sequencer Index           | N/A          | N/A             | 16-bit Register              |

| 1  | 1  | 0  | 0  | 0  | Sequencer                 | 0 x 798      | 0x0 - 0x1F      | See Table 9                  |

| 1  | 1  | 0  | 0  | 1  | Scan Bridge Support Index | N/A          | N/A             | 16-bit Register              |

| 1  | 1  | 0  | 1  | 0  |                           |              | See Table 10    |                              |

<sup>(4)</sup> The upper two bytes of each vector are ignored. These have been inserted to make the space align on long word boundaries.

### **Table 4. VECTOR STRUCTURE**

| Bit(s)      | Function                                      |  |  |

|-------------|-----------------------------------------------|--|--|

| 0x00 - 0x1F | Length (maximum of 4G)                        |  |  |

| 0x20 - 0x27 | Macro Number (1 of 256) Room for scaleability |  |  |

| 0x28 - 0x2E | Reserved                                      |  |  |

| 0x2F        | Preloaded data / Load-on-the-fly (LotF)       |  |  |

| 0x30 - 0x3F | Reserved                                      |  |  |

### Table 5. HEADER/TRAILER STRUCTURE

| Bit(s)       | Function                                 |

|--------------|------------------------------------------|

| 0x00 - 0x1F  | 32-bit count <sup>(1)</sup>              |

| 0x20 - 0x3FF | 124 bytes (992 bits) header/trailer data |

(1) Count must be greater than zero if the Header/Trailer Usage bits are not equal to "000" or "111".

### Table 6. MACRO STRUCTURE

| Bit(s)      | Function                                                                                                                                                |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x1F        | Compare                                                                                                                                                 |

| 0x1E        | Use Mask / Compare full length of vector (not including header/trailer)                                                                                 |

| 0x1D - 0x1B | Post-shift TCK_SM Count                                                                                                                                 |

| 0x1A - 0x18 | Pre-shift TCK_SM Count                                                                                                                                  |

| 0x17        | Sync Bit Support Enable                                                                                                                                 |

| 0x16        | Macro Structure Bit 8 Enable (Ignored for the shift macros with or without capture)                                                                     |

| 0x15        | Macro Structure bit 7 Enable (Ignored for the shift macros with or without capture)                                                                     |

| 0x14 - 0x12 | Header/Trailer Usage                                                                                                                                    |

| 0x11        | Macro Type bit 1                                                                                                                                        |

| 0x10        | Macro Type bit 0                                                                                                                                        |

| 0xF - 0x9   | Last 7 TMS_SM bits                                                                                                                                      |

| 0x8         | Presented during the falling edge of TCK_SM at terminal count during a Shift macro. Use in the same manner as other TMS bits for State and BIST Macros. |

| 0x7         | Loop Bit if Macro type is Shift (for 1149.1 it would be a 0) or BIST                                                                                    |

| 0x6 - 0x0   | First 7 TMS_SM Bits (LSB is first bit to be shifted out of TMS_SM)                                                                                      |

## Table 7. HEADER/TRAILER USAGE

| Bit 2 | Bit 1 | Bit 0 | Function                                |  |  |

|-------|-------|-------|-----------------------------------------|--|--|

| 0     | 0     | 0     | Ignore Headers and Trailers             |  |  |

| 0     | 0     | 1     | Use Instruction Header                  |  |  |

| 0     | 1     | 0     | Use Instruction Trailer                 |  |  |

| 0     | 1     | 1     | Jse both Instruction Header and Trailer |  |  |

| 1     | 0     | 0     | se Data Header                          |  |  |

| 1     | 0     | 1     | se Data Trailer                         |  |  |

| 1     | 1     | 0     | Jse both Data Header and Trailer        |  |  |

| 1     | 1     | 1     | Reserved                                |  |  |

## Table 8. Macro Type bits 10 and 11

| Bit 1 | Bit 0 | Function                 | Function                                                        |

|-------|-------|--------------------------|-----------------------------------------------------------------|

| 0     | 0     | BIST Macro               | Loop on loop bit for Vector count. No Data                      |

| 0     | 1     | Shift Macro              | Loop on loop bit for vector count. Read data from TDO_SM memory |

| 1     | 0     | Shift Macro with Capture | Loop on loop bit for vector count. Read data from TDO_SM memory |

| 1     | 1     | State Macro              | Do not loop on loop bit of macro. No data to be shifted         |

### **Table 9. SEQUENCER STRUCTURE**

| Bit(s)        | Function                                     |

|---------------|----------------------------------------------|

| 0x00 - 0x1F   | Sequence repeat count (up to 255)            |

| 0x20 - 0x2F   | Vector repeat count                          |

| 0x30 - 0x3F   | Vector number                                |

| XX            | Repeat vector repeat count and vector number |

| 0x3E0 - 0x3EF | Vector repeat count (up to 255)              |

| 0x3F0 - 0x3FF | Vector number (up to 63)                     |

Product Folder Links: SCANSTA101

10

### **Table 10. SCAN BRIDGE SUPPORT STRUCTURE**

| Bit(s)        | Function                                                       |

|---------------|----------------------------------------------------------------|

| 0x00 - 0x0F   | Levels of Scan Bridge support to be inserted in the scan chain |

| 0x10 - 0x17   | Hierarchical Level 0 Scan Bridge Address                       |

| 0x18 - 0x1F   | Hierarchical Level 0 Scan Bridge LSP                           |

| 0x20 - 0x27   | Hierarchical Level 1 Scan Bridge Address                       |

| 0x28 - 0x2F   | Hierarchical Level 1 Scan Bridge LSP                           |

| xx            | Hierarchical Level Scan Bridge Address and LSP                 |

| 0x7F0 - 0x7F7 | Hierarchical Level 125 Scan Bridge Address                     |

| 0x7F8 - 0x7FF | Hierarchical Level 125 Scan Bridge LSP                         |

### **MODULE DESCRIPTIONS**

Figure 1 shows a high level view of the SCANSTA101. The Parallel Processor Interface (PPI) and the Serial Scan Interface (SSI) connect to each other through a dual-port memory. The PPI provides a parallel interface for transferring data into and out of the dual-port memory, and for configuring, controlling and obtaining the status of the device. The SSI, which resides on the other side of the dual-port memory, provides the parallel-to-serial and serial-to-parallel conversion paths for providing test data and test control to support the STA Master and IEEE 1532 functions.

### **DUAL PORT MEMORY**

The Dual Port Memory module is a 2048 x 32 bit dual-port memory which acts as the buffer between the PPI and the SSI. There are seven regions of memory as viewed from the processor side. These regions, shown in Table 3, are TDO\_SM, TDI\_SM, Expected, Mask, Vector, Header/Trailer, Macro. Sequencer, and ScanBridge Support. Each has a pointer which resides in the PPI.

The memory is big endian oriented and is viewed as a single entity from the SSI side, and the SSI maintains a pointer. The dual port memory module does not include any logic outside of its own macro function, so all the timing and support logic is included in the PPI and SSI sections. There is no logic included in the SCANSTA101 design to utilize the "busy" indicators to keep the user from overwriting memory locations. The only area where this could occur in memory would be the TDI\_SM memory space since both the SSI and PPI can write to this space, but the drivers should not allow PPI writes to this area during normal operations. The Texas Instruments SCAN Ease software does not allow PPI writes to the TDI\_SM memory.

### PARALLEL PROCESSOR INTERFACE

The overall function of the PPI is to receive the parallel data from the processor; store the data in the appropriate register or memory location; act on the data if the data are PPI control data; provide status data back to the processor; and provide a read path for result data to the processor. The PPI consists of seven main blocks of logic. These blocks are the Edge Detector (ED), Processor Interface Controller (PIC), the Memory/Register Decoder (MRD), the Word/Long Word Converter (WLWC), the Control Generator (CG), the Status/Interrupt Generator (SIG) and the Flag Generator (FG).

#### WORD/LONG WORD CONVERTER

The Word/Long Word Converter (WLWC) has four 16-bit capture registers: a least significant/most significant (LS/MS) word read capture register pair; and a LS/MS word write capture register pair.

Each register within the write register pair has a separate enable to allow for the necessary control to accomplish word to long word conversions when in the 16-bit mode. In 32-bit mode, these enables are driven simultaneously. A mux is provided in front of the MS word write capture register to select between the 32-bit and 16-bit mode external bus.

Only one enable and a mux select is needed to control the read capture register pair to accomplish the long word to word conversions when in the 16- bit mode. In the 32-bit mode, the mux selection doesn't change, so 32 bits are always driven. A mux is on either side of the LS word read capture register. The mux at the register output provides for selection between the 32-bit and 16-bit mode. The mux at the register input is for selection between register space and memory space.

Copyright © 2002–2013, Texas Instruments Incorporated

All the control for this block is provided by the PIC and MRD with the 16/32-bit mode enable coming from the Setup register.

### **EDGE DETECTOR**

The PPI module can support either an asynchronous or synchronous processor interface. For an asynchronous interface, the circuit initially synchronizes STB and CE to the system clock, SCK, by pipelining these two signals through two flip-flop stages and then performing an edge detection on STB and CE. For a synchronous parallel processor interface, this circuit just performs an edge detection. The outputs of this circuit, one clock wide pulses indicating the detection of negative and positive edges, are used by the Processor Interface Controller (PIC) state machine to start and to end a processor access.

#### PROCESSOR INTERFACE CONTROLLER

The Processor Interface Controller (PIC) monitors the incoming processor control signals and sets up the appropriate internal control signals to move the data into memory or into an internal register on a write or to move the data out of memory or out of an internal register on a read. The PIC edge detects the CE and the STB to start the access. The PIC provides the control for the word to long word conversion in the WLWC by controlling the three enables and the mux select (READ\_MSW) to the capture registers. The PIC also controls when the internal read/write enable is issued to the memory to complete the read/write operation. Timing for register and memory read and write operations is described in Figure 12 and Figure 13.

#### MEMORY/REGISTER DECODER

The Memory/Register Decoder (MRD) contains all six index registers (Index, Vector Index, Header/Trailer Index, Macro Index, Sequencer Index and ScanBridge Support Index) and four address registers (TDI\_SM Address, TDO\_SM Address, Expected Address and Mask Address). On the PPI side, both index and address registers are used to maintain pointers to their respective memory spaces. The Index register sets values in all four address registers; *i.e.*, writing to the Index register sets all of the address registers. The value written to each address register is the sum of its base address and the value written to the Index register (the offset). All index and address registers except the Index register auto-increment with each access to the corresponding memory space.

The MRD provides the address decode to generate all the control and status register enables for the CG and the SIG. The MRD also provides the mux selects for the register or memory selection for the read capture operation in the WLWC.

### **CONTROL GENERATOR**

The Control Generator includes the seven control registers: the Start, Interrupt Control, Setup, Clock Divider, TDI\_SM LFSR Exponent, TDI\_SM LFSR LSB Seed, and TDI\_SM LFSR MSB Seed registers are included in this block. The CG issues a strobe to the SSI when a write has been issued to the Start or Setup registers so the SSI can react to the new control data. The strobe is derived from edge detecting the enables to the Start or Setup registers. The "new" data to the SSI are the Use Sequencer bit and three Use Vector bits from the Start register, and the TDO Default Value, TRST, ScanBridge Support Initiate/Release, three-bit Sync Bit Length, and two Test Loop-back bits from the Setup register.

### STATUS/INTERRUPT GENERATOR

The Status/Interrupt Generator comprises the four status registers plus the logic to generate the interrupts and to clear the interrupts on a read. The registers are the Status, Interrupt Status, TDI\_SM LFSR LSB Result and TDI\_SM LFSR MSB Result registers. The SIG receives the LFSR result and strobe signal SSI\_LFSR\_EN from the SSI and captures the data in the LSB and MSB registers. The SIG receives the compare result bit value from the SSI along with the compare result bit clear and the compare result bit load.

The SIG receives the 4 memory space flags from the FG along with their associated load and clear signals so these bits may be constantly updated. The half-full, half-empty, full and empty flags are generated and updated regardless of the states of their respective interrupt enables. The SIG also receives the four interrupt enables for the flags. The SIG also receives the sequencer active and the three vector active signals from the SSI. These are also updated regardless of the enable state.

If an interrupt enable is set then an interrupt will be generated. If an interrupt occurs at the same time as the interrupt status is being read, then the interrupt will be set after the read is complete. All bits in the Interrupt Status register are cleared when the register is read.

#### **FLAG GENERATOR**

The FG takes in the TDI\_SM or TDO\_SM pointer values from the PPI address pointers, compares them and generates the appropriate flags. If a flag condition has occurred, it is passed, along with the corresponding load enable, to the SIG to set the bit in the status register. If the flag condition changes, then the clear for the corresponding bit is passed to the SIG to clear the flag. The TDO\_SM empty and the TDI\_SM full flags are passed to the SSI also. A counter enable is passed from the SSI to indicate to the FG when the SSI's pointer value has changed. If a decrement and an increment occur at the same time to either of the counters, the counter value will not change.

### **PPI INTERFACE TIMING**

The processor accesses to SCANSTA101 can be classified into six categories:

- register read

- register write

- 16-bit memory read

- 16-bit memory write

- 32-bit memory read

- 32-bit memory write

Register reads and register writes are performed the same whether the device is in 16-bit mode or 32-bit mode. In 32-bit mode, only the LS word is used. The MS word is ignored. The timing for the 16-bit and 32-bit modes is exactly the same.

The 16-bit mode memory write is accomplished by performing two consecutive register writes with the only difference being that the actual write occurs on the second access. The 16-bit mode register read consists of two accesses, with the first access performed similar to the 16-bit register read but requiring one more clock to complete the memory access. Since all 32-bits of the memory data are captured on the first access, the second memory read access is 2 clocks shorter than the first.

The processor initiates a write cycle by asserting  $\overline{\text{CE}}$  followed by  $\overline{\text{STB}}$ . A set time prior to asserting  $\overline{\text{STB}}$ , the R/W is driven low and the address and data buses are driven by valid address and data, respectively. After edge detecting the  $\overline{\text{STB}}$  and registering all the inputs, the address is decoded to determine which internal address within the SCANSTA101 will be written by the processor. The  $\overline{\text{DTACK}}$  will be asserted on the same rising edge of SCK on which the negative edge of the  $\overline{\text{STB}}$  signal is detected, indicating to the processor that it can deassert the  $\overline{\text{STB}}$ . When the SCANSTA101 detects the positive edge of the  $\overline{\text{STB}}$ , it will deassert the  $\overline{\text{DTACK}}$  indicating to the processor that it can start a new cycle. The processor can start a new cycle by asserting the  $\overline{\text{STB}}$  and by driving the address and data buses with new address and data.

A read cycle is similar to the write cycle except that the  $\overline{\text{DTACK}}$  will not be asserted until the selected address location's contents are loaded. So, for a 16-bit register read it takes one more clock than it does for a write cycle.

Reads and writes to the SCANSTA101 memory require two consecutive accesses in the 16-bit external bus mode. The memory writes are similar to register writes; the processor performs two consecutive 16-bit writes to write to the selected memory location.

During a memory read, the DTACK line is not asserted until the contents of the memory is loaded into the capture registers. For this reason the first read from the memory requires five clocks which includes the memory access time, while the second read is done in three clock cycles.

### **SERIAL SCAN INTERFACE**

The Serial Scan Interface consists of the following units:

- Clock Divider and TCK\_SM Control

- TAP Tracker

- Pointer Generator

- Structure (Sequencer/Vector/Macro/ScanBridge) Decoder

Copyright © 2002–2013, Texas Instruments Incorporated

### SNLS057J-MAY 2002-REVISED APRIL 2013

- Structure (Sequencer/Vector/Macro/ScanBridge) Control Registers

- Count Generator

- Shifter (TDO\_SM/TDI\_SM/TMS\_SM)

- Comparator

- · Expected and Mask Registers

- Serial Scan Interface Controller (SSIC) and ScanBridge Controller

The clock divider unit divides the system clock SCK based on the programmable divisor set in the clock divider to generate TCK\_SM. The TCK\_SM control unit gates TCK\_SM if the TDO\_SM buffer is empty.

The TAP Tracker unit tracks the target's TAP controller state. The TAP Tracker determines whether the target's TAP controller is in SIR or SDR state, so that the necessary pad bits are inserted.

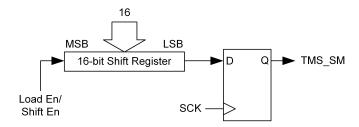

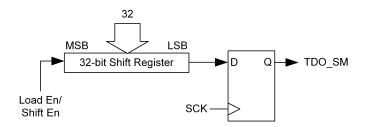

The shifter block contains two 32-bit shift registers for TDO\_SM and TDI\_SM respectively, and a 16-bit shift register for TMS\_SM.

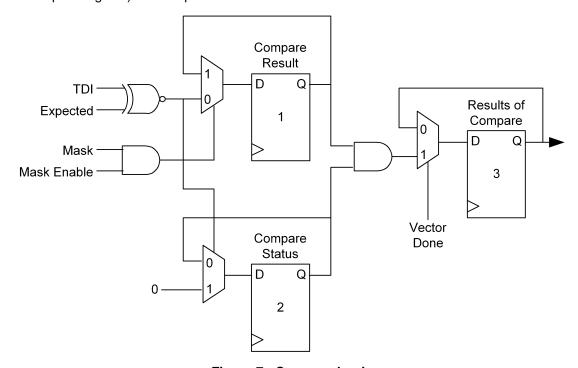

The comparator unit compares the serial input on the TDI\_SM pin with the expected data, bit by bit, if the compare bit of the Macro Structure is set. If the compare/mask bit is set, then the comparator unit compares only those bits that are unmasked.

Expected and Mask Registers contain the data fetched from the memory. This data is used by the comparator to compare the TDI\_SM input with the expected data.

The SSIC provides the timing and control signals to synchronize the operation of the various blocks in the SSI. The ScanBridge Controller consists of the control logic to set up the ScanBridge hierarchy, if the ScanBridge Support Initiate/Release bit is enabled, prior to scanning test vectors out of TDO SM.

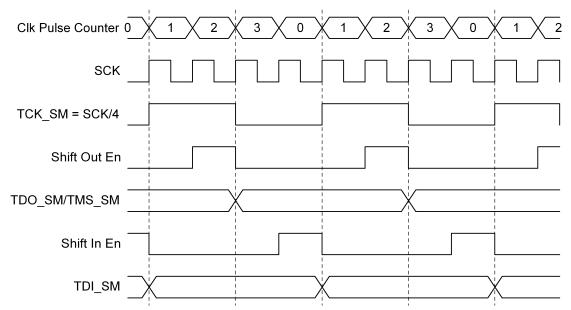

### CLOCK DIVIDER AND TCK\_SM CONTROL

The clock divider is a binary divider with only one bit of the clock divider register set to one at any given time. The SCANSTA101 SSI ignores bits 0, and 8-15 of the clock divider register, so the supported divisors are 2, 4, 8, 16, 32, 64 and 128.

To generate a TCK\_SM of frequency SCK/4, the clock divider register should be set to 4 (00000100). This will enable the gate at the output of bit 2 of the counter to generate a clock of SCK divided by 4. If in LotF mode, the TCK SM enable from the SSIC will gate TCK SM when the TDO SM buffer is empty.

#### **TAP TRACKER**

The TAP Tracker consists of a 16-bit register to track the IEEE Standard 1149.1 TAP state machine. The register is one-hot encoded (meaning that only one bit in the TAP tracker register, corresponding to the current TAP state, is set at a time) and will continuously track the target's TAP Controller based on the TMS\_SM sequence. The TAP Tracker is used by the ScanBridge support controller to determine whether the target's TAP controller is in SIR or SDR state so that it can insert an appropriate number of pre and post-shift pad bits.

The TAP Tracker will enter Test-Logic Reset state upon setting the TRST bit (bit 5) in the Setup register or by issuing a sequence of five TMS\_SM high bits.

#### **SHIFTER**

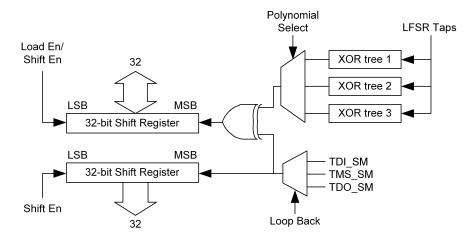

The Shifter block contains two 32-bit shift registers for TDO\_SM and TDI\_SM respectively, and one 16-bit shift register for TMS\_SM. The TMS\_SM shifter block diagram is shown in Figure 3, the TDO\_SM shifter block diagram is shown in Figure 4, and the TDI\_SM shifter block diagram is shown in Figure 5.

Before the start of a vector processing the TMS\_SM shifter is loaded with the least significant 16 bits of the macro structure. Based on the pre-shift TCK\_SM count, the TMS\_SM shifter will skip (7 - pre-shift count) least significant bits. e.g., if the pre-shift count is 4, the least significant 3 bits of the TMS\_SM shifter will not be used to drive TMS\_SM during pre-shift. Similarly, if the post-shift is less than 7 then, during post shift only the number of bits equal to the post-shift count following the macro structure bit 8 will be used to drive TMS\_SM.

Submit Documentation Feedback

Copyright © 2002–2013, Texas Instruments Incorporated

The SCANSTA101 memory is organized in big endian format. A memory write is accomplished by two consecutive writes to the same location. When embedded software loads the TDO\_SM memory, the least significant 16 bits are written first and then the most significant 16 bits. Therefore, when the Sequencer or a Vector is initialized the SSIC can directly fetch and load the long word to the TDO\_SM shifter without any modification.

Figure 3. TMS\_SM Shifter

Figure 4. TDO\_SM Shifter

Figure 5. TDI\_SM Shifter

Reading from TDI\_SM memory is accomplished by two consecutive reads. When reading from the TDI\_SM memory, the first read will contain the least significant 16 bits and the second read the most significant 16 bits.

The TDI\_SM shifter unit consists of two 32-bit shift registers as shown in Figure 5. The shift register on top in the figure is the LFSR register. Before using the TDI\_SM LFSR register, the LFSR Exponent and LFSR Seed registers must be written with valid data. The LFSR Exponent register must be written with a 3-bit binary encoded value that selects one of the five available polynomials. The value written to the LFSR Seed registers is used to initialize the TDI\_SM LFSR register to a predetermined state. Once the test vector has completely scanned in, the final contents of the LFSR register are transferred to the LFSR Result registers.

Copyright © 2002–2013, Texas Instruments Incorporated

The 32-bit shift register at the bottom is used to shift in TDI\_SM directly in normal mode or to shift in TMS\_SM or TDO\_SM in the loop-back mode. After each long word of 32 bits is shifted into this register, the contents of the register are transferred to the corresponding TDI memory location before the next shift operation.

### SHIFTER IMPLEMENTATION

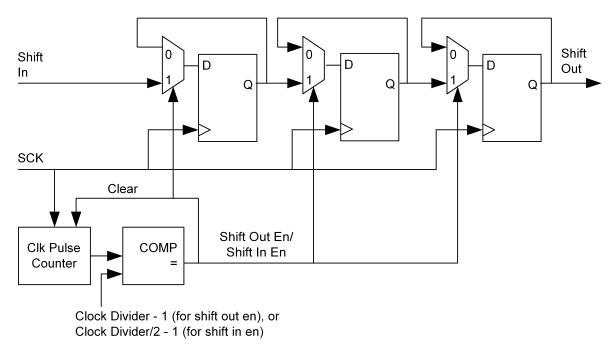

Shift register implementation is illustrated in Figure 6. Shift out enable for the TMS\_SM and TDO\_SM shifters is generated by comparing the clock pulse counter output to the clock divider - 1. Shift in enable for the TDI\_SM shifter is generated by comparing the clock pulse counter to the programmable divisor/2 - 1. These enables are gated by the control signals from SSIC so that data are shifted out (TMS\_SM/TDO\_SM) or shifted in (TDI\_SM) only when necessary.

Figure 6. Shift Register Implementation and Timing

#### **COMPARATOR AND EXPECTED/MASK REGISTERS**

The One-Bit Comparator, when enabled, compares the TDI\_SM input with expected data. When the compare feature is enabled (in preloaded vector mode only) the SSIC pre-fetches data into Expected and Mask registers from the address locations for the current vector being processed. The comparator will compare each bit on the TDI\_SM input with the corresponding bit from the expected register. If the mask feature is enabled, then the comparison is performed only on those bits that are not masked, *i.e.*, on those bits for which the mask is set to zero. Table 11 shows how the Compare and Use Mask/Compare bits in the Macro Structure are used.

Table 11. Compare and Use Mask/Compare Bit Descriptions

| Compare | Use Mask/Compare | Description          |

|---------|------------------|----------------------|

| 0       | 0                | Do Not Compare       |

| 0       | 1                | Compare with Mask    |

| 1       | 0                | Compare without Mask |

| 1       | 1                | Compare with Mask    |

The Results of Compare bit (bit 15 of Status register) stores the comparison results in the status register. This bit defaults to fail (zero) and will be updated only after the current vector is processed. In the case of a single vector the Results of Compare bit will be set to one (pass) only if all the bits in the scanned in vector match the expected vector. However, in the case of the sequencer only the results of final vector comparison will be taken into account.

Each vector within the sequencer is repeated until the vector repeat count is exhausted. The sequence is repeated until the sequencer repeat count is exhausted.

Figure 7 illustrates the compare logic.

After reset and before every sequencer process, flip-flops 1 and 3 are initialized to zero while flip-flop 2 is set to 1. When the compare feature is enabled flip-flop 1 is continuously updated with the immediate comparison results (1 for pass and 0 for fail). Flip-flop 2 is reset to zero when a mismatch occurs and remains in this state for the remainder of the current vector processing. When the current vector is completely processed flip-flop 3 (Results of Compare register) will be updated with the current status.

Figure 7. Compare Logic

#### SERIAL SCAN INTERFACE CONTROLLER AND SCANBRIDGE CONTROLLER

The Serial Scan Interface Controller (SSIC) remains in the Idle state until new data are written to the Start register. When this event occurs the following operations are performed:

- 1. If the ScanBridge Support Initiate/Release bit was not set previously and is currently set in the Setup register, the SSIC initializes the ScanBridge Controller (SBC) to perform the following steps to set up all ScanBridges in the hierarchy.

- (a) Determine the number of levels of ScanBridge support to be inserted (from the ScanBridge support structure)

- (b) Sequence TMS\_SM so that all ScanBridges in the same level of hierarchy enter the SIR state, and then shift in the address (from the ScanBridge structure) to select a ScanBridge in the current level of hierarchy. The ScanBridge's TAP controller is then sequenced through the Update-IR state.

- (c) Sequence TMS\_SM so that the selected ScanBridge's TAP controller enters the SIR state, then scan in the MODESEL instruction to put its mode register in the data path.

- (d) Sequence the selected ScanBridge's TAP controller to enter the Shift-DR state and scan in the LSP contents (from the ScanBridge structure) into its mode register. The ScanBridge's TAP controller is then sequenced through the Update-DR state.

- (e) Repeat Step 1C, but this time scan in the UNPARK instruction so that the LSP is inserted into the active scan chain.

- (f) Sequence the ScanBridge's TAP controller to enter the RTI state (the LSP will not be unparked until its TAP controller enters RTI).

- (g) Repeat Steps 1B through Step 1G to configure the ScanBridges in the remaining hierarchy levels. One set of pre-shift pad and post-shift pad bits is added to the patterns for each hierarchy level between the STA Master and the ScanBridge being configured. The pad bits are used to bypass the intermediate levels of hierarchy.

- (h) For the subsequent vectors, if the TAP Tracker enters the

- (a) SDR state, the SCANSTA101 will add one pre-shift bit for the pad register and one post-shift bit for the bypass register for each level of hierarchy.

- (b) SIR state, the SCANSTA101 will add one pre-shift bit for the pad register and eight post-shift bits for the ScanBridge instruction register for each level of hierarchy. The eight post-shift bits will be all ones, forcing the ScanBridge into bypass mode.

- (i) The pad bits need to be stripped when loading a vector into TDI\_SM. This will be done by having a status flag to indicate whether the vector that is being scanned out has ScanBridge support or not. If the scanned-out vector has ScanBridge support, then the pad bits will be stripped when the TAP Tracker enters the SDR or SIR states.

- 2. If the ScanBridge Support Initiate/Release bit was set previously and is currently reset in the Setup register, the SSIC will toggle TCK\_SM five times while TMS\_SM is held high. This will return all selected ScanBridges to the wait-for-address state and park the LSPs in the Test-Logic-Reset state. When the ScanBridge support is released the user should make sure that the Use Vector and Use Sequencer bits in the Start register are not set, so that the SSIC will not start processing a vector or the sequencer immediately after releasing the ScanBridge support. Once the ScanBridge support is released the user may start processing a vector or the sequencer by writing to the Start register.

- 3. If the sequencer is enabled (the Use Sequencer bit in the Start register is one),

- (a) Clear the Results of Compare bit and set the Using Sequencer bit in the Status register.

- (b) Fetch the sequence repeat count.

- (c) If the sequence repeat count is zero, the sequence is complete so reset the Using Sequencer bit and return to the Idle state, otherwise fetch the next vector number and its repeat count.

- (d) If the vector number is zero, decrement the sequence repeat count and return to Step 3C. If the vector number is illegal, i.e., other than 001, 010, 011, or 100, decrement the sequence repeat count and return to Step 3C.

- (e) If the vector repeat count is equal to zero, fetch the next vector number and its repeat count and go to Step 3D. If the repeat count is non-zero fetch the vector structure.

- (f) If the pre-load bit in the vector structure is not set, reset the Using Sequencer bit and return to the Idle state.

- 4. If the sequencer is not enabled but a vector is enabled (the Use Vector bits in the Start register are non-zero), fetch the current vector structure and set the appropriate Using Vector bits in the Status register. If neither the sequencer nor a vector is enabled, return to the Idle state.

- 5. Fetch the Macro Structure to be used, set the vector/macro control bits and store the TMS SM bits in the

Submit Documentation Feedback

Copyright © 2002–2013, Texas Instruments Incorporated

Structure Control registers.

- 6. If the Pre-shift TCK\_SM Count is not zero, then enable TCK\_SM and drive TMS\_SM using the first seven bits of the macro until the Pre-shift TCK\_SM Count is zero. During pre-shift, TDO\_SM will be driven with its previous value.

- 7. If the macro type is State then,

- (a) If the Macro Structure Bit 7 is enabled, set TMS\_SM to the bit 7 value of the macro structure and drive TDO\_SM with its previous value.

- (b) If the Macro Structure Bit 8 is enabled, set TMS\_SM to the bit 8 value of the macro structure and drive TDO SM with it's previous value and then go to Step 10.

- (c) If the sequencer is being used, then decrement the vector repeat count and return to Step 3E. If a vector is being used, return to the Idle state.

- 8. If the macro type is BIST then,

- (a) If the Macro Structure Bit 7 is enabled, set the count length, set TMS\_SM to the bit 7 value of the macro structure and drive TDO\_SM with the default value (Setup register bit 6) until the count length is zero.

- (b) If the Macro Structure Bit 8 is enabled, set TMS\_SM to the bit 8 value of the macro structure and drive TDO\_SM with the default value (Setup register bit 6) and then go to Step 10.

- (c) If the sequencer is being used then, decrement the vector repeat count and return to Step 3E. If a vector is being used, return to the Idle state.

- 9. If the macro type is Shift or Shift with Capture then,

- (a) If the macro type is Shift with Capture, enable TDI capture.

- (b) If the Sync Bit Support Enable bit is set, fetch sync bit count, set the count length, set TMS\_SM to the loop bit and drive the TDO\_SM high until sync bit count is zero.

- (c) If the ScanBridge Support Initiate/Release bit is set, drive the TDO\_SM with pre- PAD bit (high) and while TMS\_SM remains set to the loop bit. Repeat for each level of hierarchy.

- (d) If the Use Data/Instruction Header is enabled, fetch the header length and data, set the count length, and drive the TDO\_SM with header data until the header length is zero and while TMS\_SM remains set to the loop bit.

- (e) If the Compare or Mask/Compare is set, enable the comparator.

- (f) Set the vector count length, and drive the TDO\_SM with vector data until the count length is one and while TMS\_SM remains set to the loop bit. In the LotF mode if the count length is not zero and the TDO buffer is empty, then gate TCK\_SM until more data are available in the TDO buffer. When TCK\_SM is disabled TMS SM and TDO SM will be driven with their previous values.

- (g) If the Use Data/Instruction Trailer is enabled, fetch the trailer length and data, set the count length, and drive TDO\_SM with trailer data until the trailer length is one and while TMS\_SM remains set to the loop bit

- (h) If the ScanBridge Support Initiate/Release bit is set:

- (a) If the TAP tracker is in the Shift-IR state and the number of levels of hierarchy is greater than one, set the count length to eight, and drive TDO\_SM with post-shift pad bits (all high) until the count length is zero for each level of hierarchy and while TMS SM remains set to the loop bit.

- (b) If the TAP tracker is in the Shift-DR state and the number of levels of hierarchy is greater than one, drive TDO\_SM with a post-shift pad bit (high) for each level of hierarchy and while TMS\_SM remains set to the loop bit.

- (c) For the final level of hierarchy or if there is only one level of hierarchy, and if the TAP tracker is in the Shift-IR state, set the count length to eight, and drive TDO\_SM with post-shift pad bits (all high) until the count length is one and while TMS\_SM remains set to the loop bit.

- (i) If the Sync Bit Support Enable is set, fetch sync bit count, set the count length, and drive the TDO\_SM high until sync bit count is one and while TMS SM remains set to the loop bit.

- (j) Set TMS\_SM to bit 8 of the TMS\_SM Macro Structure sequence and drive TDO\_SM with the final vector bit or trailer bit or post-shift pad bit or sync bit. After shifting out the final vector bit, disable the comparator and register the comparison results.

- 10. If the post-shift TCK\_SM Count is not zero, then enable TCK\_SM and drive TMS\_SM using the last seven bits of the macro until the post-shift TCK\_SM Count is zero.

- 11. If the Sequencer is being used,

- (a) Decrement the sequence repeat count and return to Step 3C if the Compare or Mask/Compare is enabled and the results of compare is a fail.

- (b) Decrement the vector repeat count and return to Step 3E if the if the Compare or Mask/Compare is enabled and the results of compare is a pass.

Product Folder Links: SCANSTA101

Submit Doc

- (c) Decrement the vector repeat count and return to Step 3E if the Compare or Mask/ Compare is not enabled.

- 12. If the Vector is being used return to the Idle state.

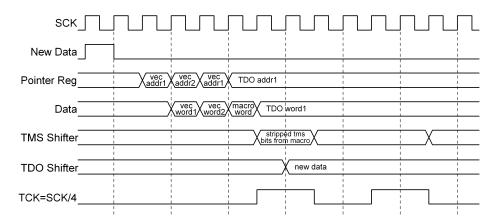

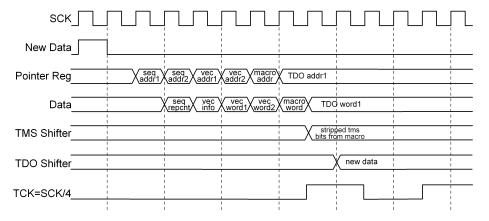

#### MODE REGISTER WRITE TO VECTOR/SEQUENCER START

Figure 8 shows the timing from the processor write to the start of vector processing. Figure 9 shows the timing from the processor write to the start of sequencer processing. A processor write to the Start registers is indicated by a "new data" pulse. On the same SCK rising edge when the "new data" is detected to be high, the Start or Setup register contents will be updated with new data. So, the decoding of the enables takes place during the next clock cycle to determine whether to process the sequencer or a vector. Therefore, one clock after the "new data" is detected, the SSIC starts loading the pointer register on consecutive cycles with the appropriate addresses to fetch the Sequencer, Vector and Macro Structures. Once the headers are decoded and Structure Control Registers are set up, the SSIC loads the pointer register so that data from the TDO\_SM memory area is fetched and loaded into the TDO\_SM shifter before being shifted out. However if there are any sync bits and/or header bits and/or ScanBridge support is enabled, then the sync bits and/or header bits and/or ScanBridge pre-PAD bits will be loaded into the TDO\_SM shifter before processing the actual test vector. Once the actual test vector is completely shifted out, again depending on the ScanBridge support and/or the use of trailers, post-PAD bits and the trailer bits are loaded and shifted out through the TDO\_SM shifter.

The count length will be decremented by one with each shift. After shifting out all the current shifter contents the shifter will be loaded with new data before the falling edge of the next TCK\_SM, if the count length is not exhausted. In the case where data cannot be loaded from the memory before the next falling edge of TCK\_SM, the TCK\_SM will be gated until the data is available.

Figure 8. Timing from Mode Register Write to Vector Start

Figure 9. Timing from Mode Register to Sequencer Start

20

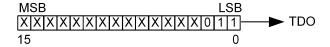

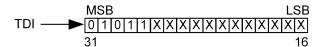

#### WRITING AND READING PARTIAL LONG WORDS

Care should be taken when writing a partial long word to TDO\_SM memory or reading a partial long word from TDI\_SM memory. Since the TDO\_SM shifter shifts out LSB first, the valid (meaningful) bits within a partial long word (i.e., long word containing less than 32 valid bits to be shifted to the scan chain) must be stored and written into the memory as the least significant bits. This will assure that the desired bits will be accurately loaded into the TDO SM shifter and shifted out to the boundary scan chain. For instance, to shift a 3-bit (110) sequence the partial long word should be written to the TDO\_SM memory as shown in Figure 10 (only the least significant 16 bits are shown). A subsequent enable and load of the vector structure with the correct length will initialize the shift operation and only the bits that are significant will be shifted out to the scan chain.

Figure 10. Writing a Partial Long Word to the TDO\_SM Memory