# 12-Bit, 1MSPS, 4-/8-Channel, Bipolar-Input, SAR Analog-to-Digital Converter with Software-Selectable Ranges

Check for Samples: ADS8634, ADS8638

#### **FEATURES**

- Selectable Input Range: ±10V, ±5V, ±2.5V, 0V to 10V, or 0V to 5V

Up to ±12V with External Reference

- No Latent Conversions Up to 1MSPS

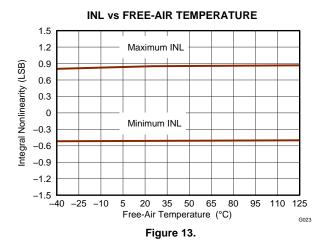

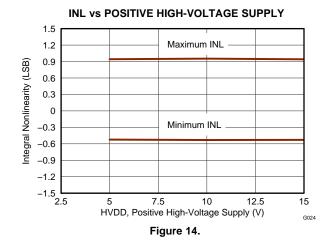

- Outstanding Performance: 12 Bits No Missing Codes INL: ±0.9LSB SNR: 71.8dB

- Highly Integrated:

4- or 8-Channel Input Mux

Temperature Sensor

Internal Voltage Reference

Alarm Thresholds for Each Channel

- Low Power:

14.45mW at 1MSPS

5.85mW at 0.1MSPS

Flexible Power-Down Mode

- SPI™-Compatible Serial Interface

- Extended Temperature Range: -40°C to +125°C

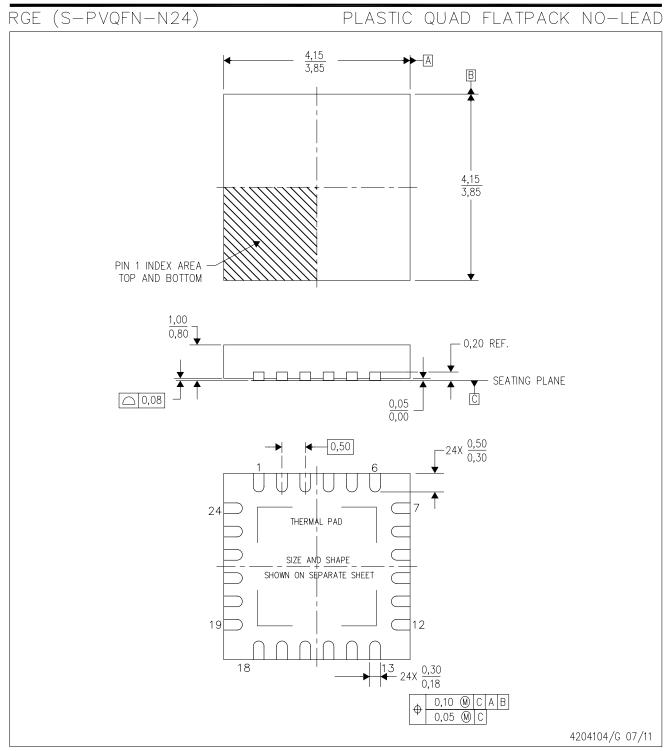

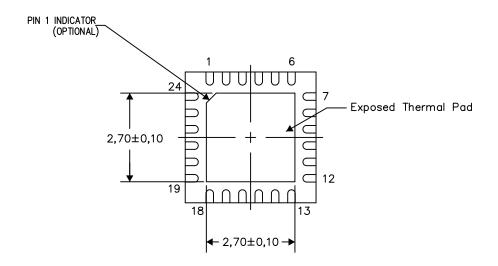

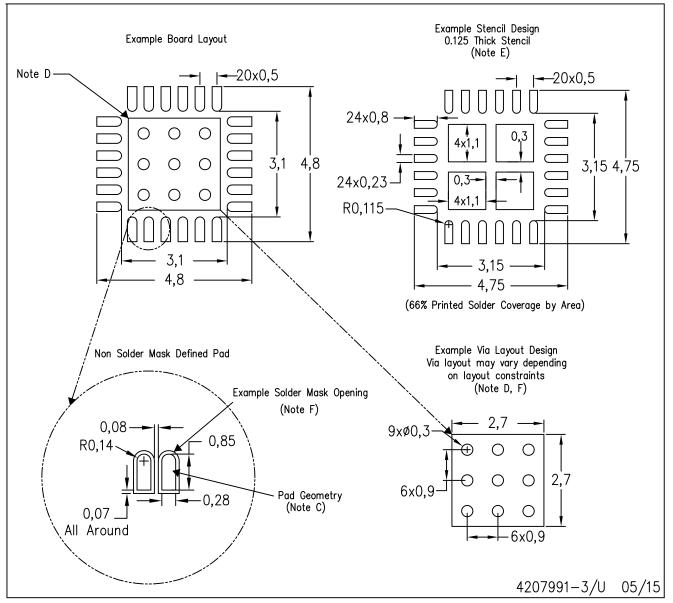

- Small Footprint: 4mm × 4mm QFN Package

#### **APPLICATIONS**

- Industrial Process Controls (PLC)

- · Data Acquisition Systems

- High-Speed, Closed-Loop Systems

- Digital Power Supplies

#### **DESCRIPTION**

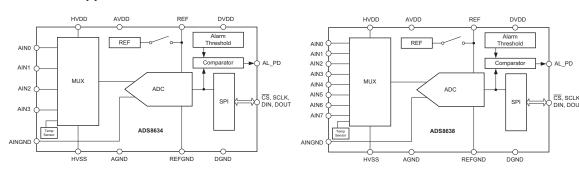

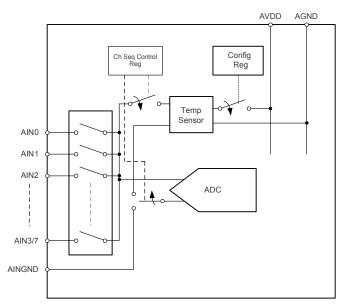

The ADS8634 and ADS8638 (ADS8634/8) are 12-bit analog-to-digital converters (ADCs) capable of measuring inputs up to ±10V at 1MSPS. Using a successive approximation register (SAR) core, these ADCs provide a sample-and-hold front-end with no latency in conversions. The ADS8634 includes an input multiplexer (mux) for measuring up to four inputs. The ADS8638 can measure up to eight inputs.

In addition to the input multiplexer, the ADS8634/8 feature an internal temperature sensor, voltage reference, and a digital comparator for setting alarm thresholds on each input; therefore, a minimal amount of external components are required. A simple SPI-compatible interface provides for communication and control. The digital supply operates from 5V all the way down to 1.8V for direct connection to a wide range of processors and controllers.

Ideal for demanding industrial measurement applications, the ADS8634/8 are fully specified over the extended industrial temperature range of -40°C to +125°C and are available in a small form-factor QFN-24 package.

M

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

SPI is a trademark of Motorola.

All other trademarks are the property of their respective owners.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### **DEVICE COMPARISON<sup>(1)</sup>**

| PRODUCT | RESOLUTION | CHANNELS | SAMPLE RATE |

|---------|------------|----------|-------------|

| ADS8634 | 40 PH      | 4        | AMCDC       |

| ADS8638 | 12-Bit     | 8        | 1MSPS       |

<sup>(1)</sup> For the most current package and ordering information, see the Package Option Addendum at the end of this document, or visit the device product folder at <a href="https://www.ti.com">www.ti.com</a>.

#### **ABSOLUTE MAXIMUM RATINGS**

Over operating free-air temperature range, unless otherwise noted. (1)

|                           |                            | VALUE                    | UNIT |

|---------------------------|----------------------------|--------------------------|------|

| AINn to AGND or AIN       | GND to AGND                | HVSS - 0.3 to HVDD + 0.3 | V    |

| AVDD to AGND or DV        | /DD to DGND                | -0.3 to 7                | V    |

| HVDD to AGND              |                            | -0.3 to 18               | V    |

| HVSS to AGND              |                            | -18 to 0.3               | V    |

| HVDD to HVSS              |                            | -0.3 to 33               | V    |

| Digital input voltage to  | DGND                       | -0.3 to DVDD + 0.3       | V    |

| Digital output to DGNI    | )                          | -0.3 to DVDD + 0.3       | V    |

| Operating temperature     | e range                    | -40 to +125              | °C   |

| Storage temperature range |                            | -65 to +150              | °C   |

| ESD ratings, all pins     | Human body model (HBM)     | ±2000                    | V    |

|                           | Charged device model (CDM) | ±500                     | V    |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute—maximum—rated conditions for extended periods may affect device reliability. These are stress ratings only and functional operation of the device at these or any other conditions beyond those specified in the Electrical Characteristics table is not implied.

#### **ELECTRICAL CHARACTERISTICS: ADS8634, ADS8638**

Minimum/maximum specifications at  $T_A = -40^{\circ}\text{C}$  to +125°C,  $f_{\text{SAMPLE}} = 1\text{MSPS}$ , HVDD = 10V to 15V, HVSS = -10V to -15V, AVDD = 4.75V to 5.25V, DVDD = 2.7V to 3.6V, and  $V_{\text{REF}} = 2.5\text{V}$ , unless otherwise noted. Typical specifications at +25°C,  $f_{\text{SAMPLE}} = 1\text{MHz}$ , HVDD = 10V, HVSS = -10V, AVDD = 3.3V, DVDD = 3.3V, and  $V_{\text{REF}} = 2.5\text{V}$ , unless otherwise noted.

|                             |                        |                                                                                                                                               | ADS  | 8634, ADS863 | 8    |                    |

|-----------------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|------|--------------|------|--------------------|

| PAR                         | AMETER                 | TEST CONDITIONS                                                                                                                               | MIN  | TYP          | MAX  | UNIT               |

| ANALOG INPUT                |                        |                                                                                                                                               |      |              |      |                    |

|                             |                        |                                                                                                                                               |      | ±2.5         |      | V                  |

|                             |                        | Bipolar ranges, V <sub>REF</sub> = 2.5V                                                                                                       |      | ±5           |      | V                  |

| Full-scale input sp         | oan <sup>(1)</sup>     |                                                                                                                                               |      | ±10          |      | V                  |

|                             |                        | V 05V                                                                                                                                         |      | 0 to 5       |      | V                  |

|                             |                        | Unipolar ranges, V <sub>REF</sub> = 2.5V                                                                                                      |      | 0 to 10      |      | V                  |

| AINx absolute inp           | ut range               |                                                                                                                                               | HVSS |              | HVDD | V                  |

| AINGND absolute             | input range            |                                                                                                                                               | -0.2 |              | 0.2  | V                  |

| Input capacitance           | l                      |                                                                                                                                               |      | 8            |      | pF                 |

| Input leakage cur           | rent                   | At +125°C                                                                                                                                     |      | 200          |      | nA                 |

| SYSTEM PERFO                | RMANCE                 | 1                                                                                                                                             |      |              |      |                    |

| Resolution                  |                        |                                                                                                                                               |      | 12           |      | Bits               |

| No missing codes            | <b>;</b>               |                                                                                                                                               | 12   |              |      | Bits               |

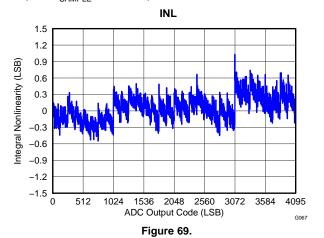

| Integral linearity          |                        |                                                                                                                                               | -1.5 | +0.9/-0.9    | 1.5  | LSB <sup>(2)</sup> |

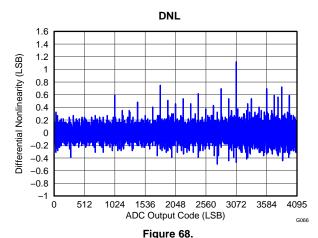

| Differential lineari        | ty                     |                                                                                                                                               | -1.0 | +0.9/-0.5    | 1.6  | LSB                |

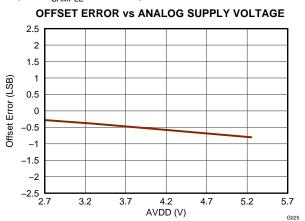

| Offset error <sup>(3)</sup> |                        |                                                                                                                                               | -3   | ±0.8         | 3    | LSB                |

| Offset error drift          |                        |                                                                                                                                               |      | 0.75         |      | ppmFS/°C           |

| Gain error <sup>(5)</sup>   |                        |                                                                                                                                               | -8   | ±2           | 8    | LSB                |

| Gain error drift            |                        |                                                                                                                                               |      | 1.2          |      | ppm/°C             |

| Noise                       |                        |                                                                                                                                               |      | 0.33         |      | LSB                |

| Power-supply reje           | ection                 | At FFCh output code with 250mV <sub>PP</sub> and 480Hz ripple on AVDD                                                                         |      | -87          |      | dB                 |

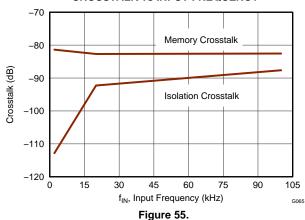

| Crosstalk                   | Isolation<br>crosstalk | Crosstalk on channel 0 with channel 0 permanently selected, 2kHz full-scale sine wave on channel 1, all other channels grounded               |      | -110         |      | dB                 |

| Memory crosstalk            |                        | Crosstalk on channel 0, 2kHz full-scale sine wave on channel 1, all other channels grounded, device scans channel 0 and channel 1 alternately |      | -81          |      | dB                 |

| SAMPLING DYN                | AMICS                  |                                                                                                                                               |      |              |      |                    |

| Conversion time             |                        | At 20MHz SCLK, DVDD = 2.7V to 5.25V                                                                                                           |      |              | 750  | ns                 |

| Acquisition time            |                        | AVDD = 2.7V to 5.25V                                                                                                                          | 250  |              |      | ns                 |

| Maximum through             | nput rate              | At 20MHz SCLK, DVDD = 2.7V to 5.25V                                                                                                           |      | 1            | 1    | MSPS               |

| Aperture delay              |                        |                                                                                                                                               |      | 13           |      | ns                 |

| Step response               |                        |                                                                                                                                               |      | 250          |      | ns                 |

|                             |                        |                                                                                                                                               |      |              |      |                    |

<sup>(1)</sup> Ideal input span; does not include gain or offset error.

<sup>(2)</sup> LSB means least significant bit.

<sup>(3)</sup> Measured relative to an ideal full-scale input.

<sup>(4)</sup> ppmFS/°C is drift measured in parts per million of full-scale range per degree centigrade.

<sup>5)</sup> Does not include reference drift.

# **ELECTRICAL CHARACTERISTICS: ADS8634, ADS8638 (continued)**

Minimum/maximum specifications at  $T_A = -40^{\circ}\text{C}$  to +125°C,  $f_{\text{SAMPLE}} = 1\text{MSPS}$ , HVDD = 10V to 15V, HVSS = -10V to -15V, AVDD = 4.75V to 5.25V, DVDD = 2.7V to 3.6V, and  $V_{\text{REF}} = 2.5\text{V}$ , unless otherwise noted. Typical specifications at +25°C,  $f_{\text{SAMPLE}} = 1\text{MHz}$ , HVDD = 10V, HVSS = -10V, AVDD = 3.3V, DVDD = 3.3V, and  $V_{\text{REF}} = 2.5\text{V}$ , unless otherwise noted.

| SAIVII EE ,                          |                   |                                                   | ADS86    | 34, ADS86 | 38                                      |          |

|--------------------------------------|-------------------|---------------------------------------------------|----------|-----------|-----------------------------------------|----------|

| PARA                                 | METER             | TEST CONDITIONS                                   | MIN      | TYP       | MAX                                     | UNIT     |

| DYNAMIC CHARA                        | CTERISTICS        |                                                   |          |           |                                         |          |

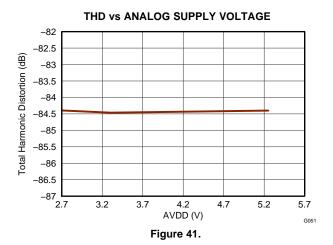

| T-4-1 b i - di-4                     | :(6) (TUD)        | At 1kHz                                           |          | -81       |                                         | dB       |

| Total harmonic distortion (6) (THD)  |                   | At 100kHz                                         |          | -80       |                                         | dB       |

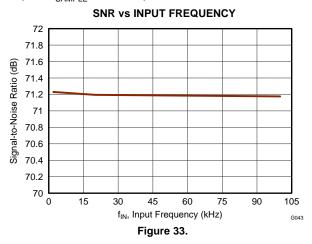

| Cianal ta naiga ratio                | (CND)             | At 1kHz                                           | 71       | 71.8      |                                         | dB       |

| Signal-to-noise ration               | (SNK)             | At 100kHz                                         |          | 71.1      |                                         | dB       |

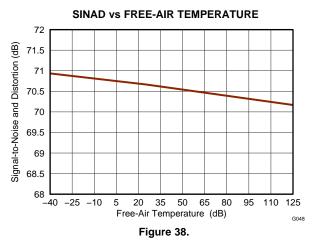

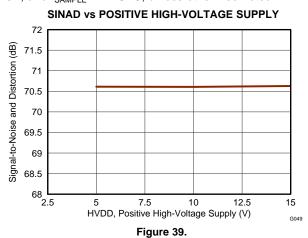

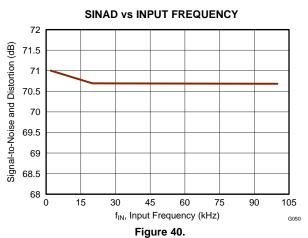

| Signal-to-noise and                  | distortion ratio  | At 1kHz                                           | 70.1     | 71.3      |                                         | dB       |

| (SINAD)                              |                   | At 100kHz                                         |          | 70.5      |                                         | dB       |

| On win on the state of               | : (OEDD)          | At 1kHz                                           |          | -83       |                                         | dB       |

| Spurious-free dynar                  | file range (SFDR) | At 100kHz                                         |          | -80       |                                         | dB       |

| Full-power bandwid                   | th                | At –3dB                                           |          | 1         |                                         | MHz      |

| DIGITAL INPUT/O                      | JTPUT             |                                                   |          |           |                                         |          |

| Logic family                         |                   |                                                   |          | CMOS      |                                         | V        |

|                                      | V <sub>IH</sub>   |                                                   | 0.7 DVDD |           |                                         | V        |

| La sia la cal                        | V <sub>IL</sub>   |                                                   |          |           | 0.3 DVDD                                | V        |

| Logic level                          | V <sub>OH</sub>   | With 20pF load on SDO                             | 0.8 DVDD |           |                                         | V        |

|                                      | V <sub>OL</sub>   | With 20pF load on SDO                             |          |           | 0.2 DVDD                                | V        |

| EXTERNAL VOLTA                       | AGE REFERENCE     |                                                   |          |           |                                         |          |

| Reference input voltage range        | $V_{REF}$         |                                                   | 2.0      |           | 3.0 or<br>AVDD,<br>whichever<br>is less | ٧        |

| INTERNAL VOLTA                       | GE REFERENCE      |                                                   |          |           |                                         |          |

| Reference output ve                  | oltage            |                                                   |          | 2.5       |                                         | V        |

| Initial accuracy                     |                   |                                                   | -1.2     |           | 1.2                                     | %        |

| Temperature drift                    |                   |                                                   |          | 20        |                                         | ppm/°C   |

| Drive current, source <sup>(7)</sup> |                   |                                                   |          |           | 750                                     | μΑ       |

| Drive current, sink                  |                   |                                                   |          |           | 20                                      | μΑ       |

| Driver output imped                  | ance              |                                                   |          | 1         |                                         | Ω        |

| Turn-on settling tim                 | e                 | With 10µF decoupling capacitor from REF to REFGND |          | 9         |                                         | ms       |

| INTERNAL TEMPE                       | RATURE SENSOR     |                                                   |          |           |                                         |          |

| Absolute accuracy                    |                   |                                                   |          | 5         |                                         | % of FSR |

<sup>(6)</sup> Calculated on the first nine harmonics of the input frequency.

<sup>(7)</sup> Internal reference output is short-circuit protected. In case of short-circuit to ground, the drive current is limited to this value.

### **ELECTRICAL CHARACTERISTICS: ADS8634, ADS8638 (continued)**

$\label{eq:maximum} \begin{tabular}{ll} Minimum/maximum specifications at $T_A = -40^{\circ}$C to $+125^{\circ}$C, $f_{SAMPLE} = 1MSPS, HVDD = 10V$ to $15V$, HVSS = $-10V$ to $-15V$, $AVDD = 4.75V$ to $5.25V$, DVDD = $2.7V$ to $3.6V$, and $V_{REF} = 2.5V$, unless otherwise noted. Typical specifications at $+25^{\circ}$C, $f_{SAMPLE} = 10V$ to $15V$, $f_{SAMPLE} = 10V$ to $$ f<sub>SAMPLF</sub> = 1MHz, HVDD = 10V, HVSS = -10V, AVDD = 3.3V, DVDD = 3.3V, and V<sub>RFF</sub> = 2.5V, unless otherwise noted.

|                                        |                             |                                                                                                                                   | ADS86 | 34, ADS863 | 3    |      |

|----------------------------------------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------|------------|------|------|

| PARAI                                  | METER                       | TEST CONDITIONS                                                                                                                   | MIN   | TYP        | MAX  | UNIT |

| POWER-SUPPLY R                         | REQUIREMENTS                |                                                                                                                                   |       |            |      |      |

|                                        | V <sub>AVDD</sub>           |                                                                                                                                   | 2.7   | 3.3        | 5.25 | V    |

| Cunnly valtage                         | $V_{DVDD}$                  |                                                                                                                                   | 1.65  | 3.3        | 5.25 | V    |

| Supply voltage                         | V <sub>HVDD</sub>           | 10V < V <sub>HVDD</sub> - V <sub>HVSS</sub> < 30V                                                                                 | 5     | 10         | 15   | V    |

|                                        | V <sub>HVSS</sub>           | 10V < V <sub>HVDD</sub> - V <sub>HVSS</sub> < 30V                                                                                 | -15   | -10        | 0    | V    |

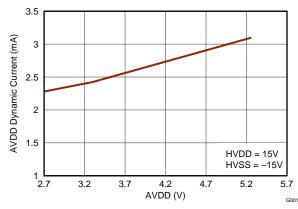

|                                        |                             | At V <sub>AVDD</sub> = 2.7V to 3.6V and 1MHz throughput, normal mode with internal reference and temperature sensor off           |       | 2.5        |      | mA   |

|                                        | I <sub>AVDD</sub> (dynamic) | At $V_{\text{AVDD}} = 4.75 \text{V}$ to 5.25V and 1MHz throughput, normal mode with internal reference and temperature sensor off |       | 3.1        | 3.6  | mA   |

| AVDD supply                            |                             | At $V_{\text{AVDD}}$ = 2.7V to 3.6V and SCLK off, normal mode with internal reference and temperature sensor off                  |       | 1.45       |      | mA   |

| current                                | I <sub>AVDD</sub> (static)  | At $V_{\text{AVDD}} = 4.75 \text{V}$ to 5.25V and SCLK off, normal mode with internal reference and temperature sensor off        |       | 1.5        | 1.9  | mA   |

|                                        | I <sub>AVDD(ref)</sub> (8)  | At $V_{\text{AVDD}}$ = 2.7V to 5.25V, additional AVDD current with internal reference on and temperature sensor off               |       | 180        |      | μΑ   |

|                                        | I <sub>AVDD(temp)</sub> (9) | At $V_{\text{AVDD}}$ = 2.7V to 5.25V, additional AVDD current with internal temperature sensor on and internal reference off      |       | 400        |      | μA   |

| HVDD supply                            | I <sub>HVDD(dynamic)</sub>  | HVDD = 15V and 1MSPS throughput                                                                                                   |       | 270        | 350  | μΑ   |

| current                                | I <sub>HVDD(static)</sub>   | HVDD = 15V and device static with SCLK off                                                                                        |       | 5          |      | μΑ   |

| HVSS supply                            | I <sub>HVSS(dynamic)</sub>  | HVSS = -15 V and 1MSPS throughput                                                                                                 |       |            | 520  | μΑ   |

| current                                | I <sub>HVSS(static)</sub>   | HVSS = -15V and device static with SCLK off                                                                                       |       | 5          |      | μΑ   |

| DVDD supply<br>current <sup>(10)</sup> | I <sub>DVDD</sub>           | DVDD = 3.3V, f <sub>SAMPLE</sub> = 1MSPS, DOUT load = 20pF                                                                        |       | 2.5        |      | mA   |

|                                        | A)/DD                       | SCLK off, internal reference and temperature sensor off                                                                           |       | 10         |      | μΑ   |

| Power-down state                       | AVDD current                | SCLK on, internal reference and temperature sensor off                                                                            |       | 160        |      | μA   |

|                                        | HVDD current                |                                                                                                                                   |       | 5          |      | μA   |

|                                        | HVSS current                |                                                                                                                                   |       | 5          |      | μA   |

| TEMPERATURE RA                         | ANGE                        |                                                                                                                                   |       |            |      |      |

| Specified performan                    | ice                         |                                                                                                                                   | -40   |            | +125 | °C   |

$<sup>\</sup>label{eq:Add_lav_DD_(ref)} \mbox{ Add } \mbox{$I_{AVDD(static)}$ (as applicable), if internal reference is selected.}$

### THERMAL INFORMATION

|                  |                                              | ADS8634/8RGE |       |

|------------------|----------------------------------------------|--------------|-------|

|                  | THERMAL METRIC <sup>(1)</sup>                | RGE          | UNITS |

|                  |                                              | 24 PINS      |       |

| $\theta_{JA}$    | Junction-to-ambient thermal resistance       | 32.6         |       |

| $\theta_{JCtop}$ | Junction-to-case (top) thermal resistance    | 30.5         |       |

| $\theta_{JB}$    | Junction-to-board thermal resistance         | 3.3          | °C/W  |

| ΨЈТ              | Junction-to-top characterization parameter   | 0.4          | C/VV  |

| ΨЈВ              | Junction-to-board characterization parameter | 9.3          |       |

| $\theta_{JCbot}$ | Junction-to-case (bottom) thermal resistance | 2.6          |       |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

<sup>(9)</sup> Add I<sub>AVDD(temp)</sub> to I<sub>AVDD(dynamic)</sub> or I<sub>AVDD(static)</sub> (as applicable), if internal temperature sensor is enabled.

(10) I<sub>DVDD</sub> consumes only dynamic current. I<sub>DVDD</sub> = C<sub>LOAD</sub> × V<sub>DVDD</sub> × number of 0 → 1 transitions in DOUT × f<sub>SAMPLE</sub>. I<sub>DVDD</sub> is a load-dependent current; there is no current when the output is not toggling.

#### PARAMETER MEASUREMENT INFORMATION

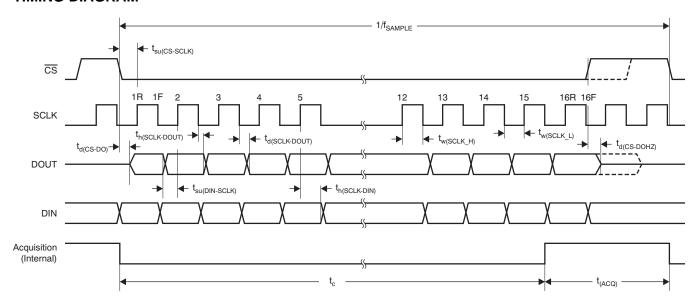

#### **TIMING DIAGRAM**

Table 1. Timing Requirements (1)(2)(3)

|                           |                                                  | TEST        | ADS86 | 34, ADS8638 |      |      |

|---------------------------|--------------------------------------------------|-------------|-------|-------------|------|------|

|                           | PARAMETER                                        | CONDITIONS  | MIN   | TYP         | MAX  | UNIT |

|                           |                                                  | DVDD = 1.8V |       |             | 15   | SCLK |

| t <sub>c</sub>            | Conversion time                                  | DVDD = 3V   |       |             | 15   | SCLK |

|                           |                                                  | DVDD = 5V   |       |             | 15   | SCLK |

|                           |                                                  | DVDD = 1.8V | 250   |             |      | ns   |

| t <sub>(ACQ)</sub>        | Acquisition time                                 | DVDD = 3V   | 250   |             |      | ns   |

|                           |                                                  | DVDD = 5V   | 250   |             |      | ns   |

|                           |                                                  | DVDD = 1.8V |       |             | 52.5 | ns   |

| t <sub>d(CS-DO)</sub>     | Delay time, CS low to first data (D0 to D15) out | DVDD = 3V   |       |             | 40.0 | ns   |

|                           |                                                  | DVDD = 5V   |       |             | 30.5 | ns   |

|                           |                                                  | DVDD = 1.8V | 26.0  |             |      | ns   |

| t <sub>su(CS-SCLK)</sub>  | Setup time, CS low to first SCLK rising edge     | DVDD = 3V   | 18.5  |             |      | ns   |

|                           |                                                  | DVDD = 5V   | 15.5  |             |      | ns   |

|                           |                                                  | DVDD = 1.8V |       |             | 51.5 | ns   |

| t <sub>d(SCLK-DOUT)</sub> | Delay time, SCLK falling to DOUT                 | DVDD = 3V   |       |             | 33.0 | ns   |

|                           |                                                  | DVDD = 5V   |       |             | 25.3 | ns   |

|                           |                                                  | DVDD = 1.8V | 5.5   |             |      | ns   |

| t <sub>h(SCLK-DOUT)</sub> | Hold time, SCLK falling to DOUT valid            | DVDD = 3V   | 5.0   |             |      | ns   |

|                           |                                                  | DVDD = 5V   | 4.7   |             |      | ns   |

|                           |                                                  | DVDD = 1.8V | 7.3   |             | 31.0 | ns   |

| t <sub>d(CS-DOHZ)</sub>   | Delay time CS high to DOUT high-z                | DVDD = 3V   | 6.4   |             | 22.0 | ns   |

|                           |                                                  | DVDD = 5V   | 5.9   |             | 16.4 | ns   |

<sup>(1)</sup> All specifications at -40°C to +125°C, unless otherwise noted.

<sup>(2) 1.8</sup>V specifications apply from 1.65V to 1.95V; 3V specifications apply from 2.7V to 3.6V; and 5V specifications apply from 4.75V to 5.25V.

<sup>(3)</sup> With 20pF load on DOUT.

# PARAMETER MEASUREMENT INFORMATION (continued)

Table 1. Timing Requirements<sup>(1)(2)(3)</sup> (continued)

|                           |                                                | TEST        | ADS86 | 34, ADS8638 |      |

|---------------------------|------------------------------------------------|-------------|-------|-------------|------|

|                           | PARAMETER                                      | CONDITIONS  | MIN   | TYP MAX     | UNIT |

|                           |                                                | DVDD = 1.8V | 7.0   |             | ns   |

| t <sub>su(DIN-SCLK)</sub> | Setup time, DIN valid to SCLK rising edge      | DVDD = 3V   | 6.0   |             | ns   |

|                           |                                                | DVDD = 5V   | 5.0   |             | ns   |

|                           |                                                | DVDD = 1.8V | 9.0   |             | ns   |

| t <sub>h(SCLK-DIN)</sub>  | (SCLK-DIN) Hold time, SCLK rising to DIN valid | DVDD = 3V   | 8.0   |             | ns   |

|                           |                                                | DVDD = 5V   | 7.0   |             | ns   |

|                           |                                                | DVDD = 1.8V | 25    |             | ns   |

| W(SCLK_H)                 | Pulse duration, SCLK high                      | DVDD = 3V   | 20    |             | ns   |

|                           |                                                | DVDD = 5V   | 20    |             | ns   |

|                           |                                                | DVDD = 1.8V | 25    |             | ns   |

| W(SCLK_L)                 | Pulse duration, SCLK low                       | DVDD = 3V   | 20    |             | ns   |

|                           |                                                | DVDD = 5V   | 20    |             | ns   |

|                           |                                                | DVDD = 1.8V |       | 16          | MHz  |

| SCLK                      | SCLK frequency                                 | DVDD = 3V   |       | 20          | MHz  |

|                           |                                                | DVDD = 5V   |       | 20          | MHz  |

|                           |                                                | DVDD = 1.8V |       | 0.84        | MSPS |

| f <sub>SAMPLE</sub> Sai   | Sampling frequency                             | DVDD = 3V   |       | 1           | MSPS |

|                           |                                                | DVDD = 5V   |       | 1           | MSPS |

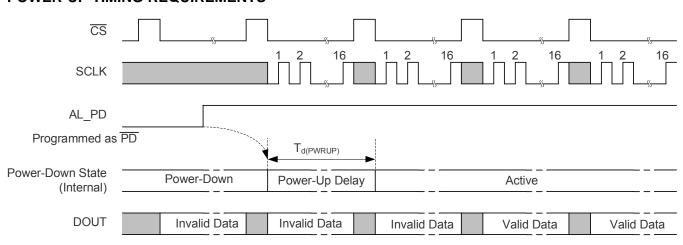

### **POWER-UP TIMING REQUIREMENTS**

Table 2. TIMING REQUIREMENTS(1)

|                           |                                                         |     | 34, ADS8638 |     |            |

|---------------------------|---------------------------------------------------------|-----|-------------|-----|------------|

|                           | PARAMETER                                               | MIN | TYP         | MAX | UNIT       |

| t <sub>d(PWRUP)</sub> (2) | Power-up delay from first CS after power-up command     |     |             | 1   | μs         |

|                           | Invalid conversions after device is active (powered up) |     |             | 1   | Conversion |

<sup>(1)</sup> All specifications at -40°C to +125°C, unless otherwise noted.

<sup>(2)</sup> Power-up time excludes internal reference and temperature sensor.

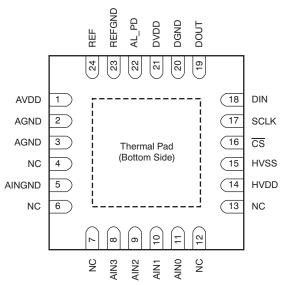

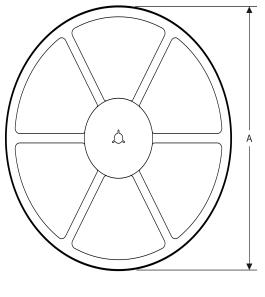

#### **PIN CONFIGURATIONS**

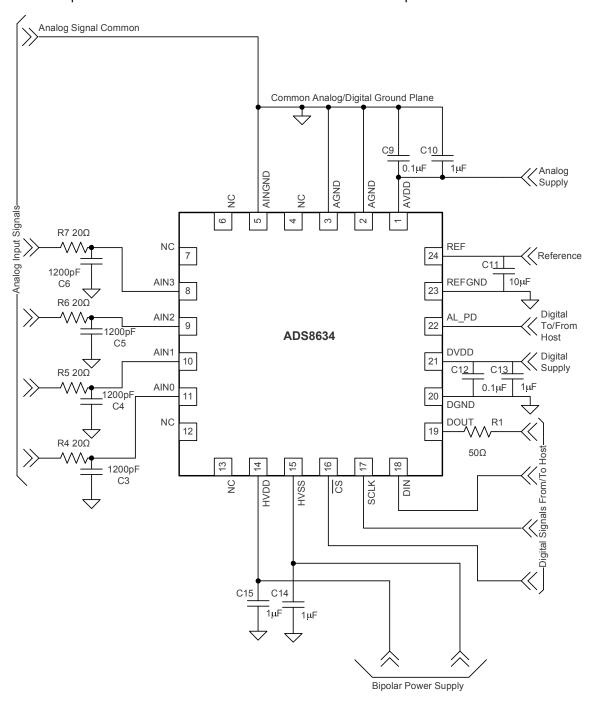

Figure 1. ADS8634 Pin Configuration

#### **ADS8634 PIN ASSIGNMENTS**

| PIN NUMBER      | NAME   | FUNCTION                  | DESCRIPTION                                                                                                                                                                                                                                                                      |

|-----------------|--------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1               | AVDD   | Analog power supply       | Analog power supply                                                                                                                                                                                                                                                              |

| 2, 3            | AGND   | Analog power supply       | Analog ground                                                                                                                                                                                                                                                                    |

| 4, 6, 7, 12, 13 | NC     | _                         | These pins are not internally connected; do not float these pins. It is recommended to connect these pins to AGND.                                                                                                                                                               |

| 5               | AINGND | Input                     | Common for all analog input channels; acts as ground sense terminal                                                                                                                                                                                                              |

| 8               | AIN3   | Analog input              | Analog input channel 3                                                                                                                                                                                                                                                           |

| 9               | AIN2   | Analog input              | Analog input channel 2                                                                                                                                                                                                                                                           |

| 10              | AIN1   | Analog input              | Analog input channel 1                                                                                                                                                                                                                                                           |

| 11              | AIN0   | Analog input              | Analog input channel 0                                                                                                                                                                                                                                                           |

| 14              | HVDD   | High-voltage power supply | High-voltage positive supply for multiplexer channels                                                                                                                                                                                                                            |

| 15              | HVSS   | High-voltage power supply | High-voltage negative supply for multiplexer channels                                                                                                                                                                                                                            |

| 16              | CS     | Digital input             | Chip select input                                                                                                                                                                                                                                                                |

| 17              | SCLK   | Digital input             | Serial clock input                                                                                                                                                                                                                                                               |

| 18              | DIN    | Digital input             | Serial data input                                                                                                                                                                                                                                                                |

| 19              | DOUT   | Digital output            | Serial data output                                                                                                                                                                                                                                                               |

| 20              | DGND   | Digital power supply      | Digital ground                                                                                                                                                                                                                                                                   |

| 21              | DVDD   | Digital power supply      | Digital I/O supply                                                                                                                                                                                                                                                               |

|                 |        | Digital output            | Active high, output indicates alarm (programmed as an output pin)                                                                                                                                                                                                                |

| 22              | AL_PD  | Digital input             | Active low, asynchronous power-down.  The device features an internal, weak pull-up resistor from the AL_PD pin to DVDD. The AL_PD pin can also be floated when programmed as a power-down input.  (The default condition for this pin is programmed as a power-down input pin.) |

| 23              | REFGND | Analog input              | Reference ground input to device when an external reference is selected. This pin acts as a reference decoupling ground terminal when an internal reference is selected.                                                                                                         |

| 24              | REF    | Analog input              | Reference input to device when an external reference is selected. This pin acts as a reference decoupling terminal when an internal reference is selected.                                                                                                                       |

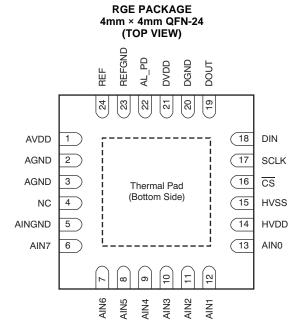

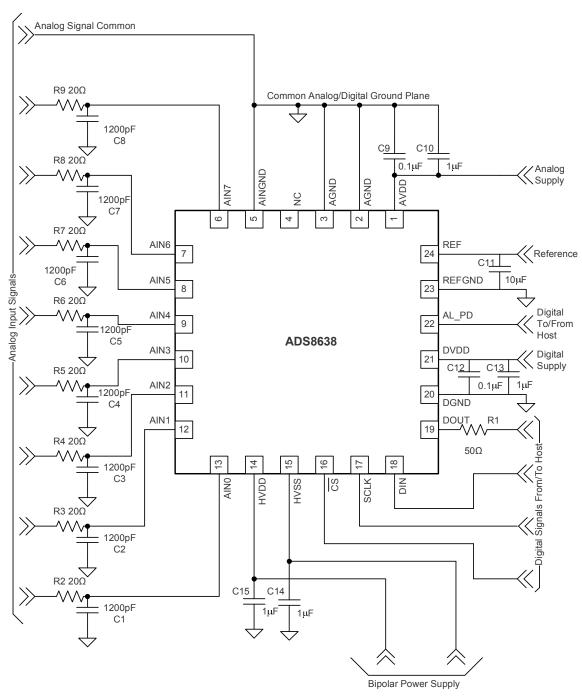

Figure 2. ADS8638 Pin Configuration

### **ADS8638 PIN ASSIGNMENTS**

| PIN NUMBER | NAME   | FUNCTION                  | DESCRIPTION                                                                                                                                                             |

|------------|--------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | AVDD   | Analog power supply       | Analog power supply                                                                                                                                                     |

| 2, 3       | AGND   | Analog power supply       | Analog ground                                                                                                                                                           |

| 4          | NC     | _                         | This pin is not internally connected; do not float this pin. It is recommended to connect this pin to AGND.                                                             |

| 5          | AINGND | Input                     | Common for all analog input channels; acts as ground sense terminal                                                                                                     |

| 6          | AIN7   | Analog input              | Analog input channel 7                                                                                                                                                  |

| 7          | AIN6   | Analog input              | Analog input channel 6                                                                                                                                                  |

| 8          | AIN5   | Analog input              | Analog input channel 5                                                                                                                                                  |

| 9          | AIN4   | Analog input              | Analog input channel 4                                                                                                                                                  |

| 10         | AIN3   | Analog input              | Analog input channel 3                                                                                                                                                  |

| 11         | AIN2   | Analog input              | Analog input channel 2                                                                                                                                                  |

| 12         | AIN1   | Analog input              | Analog input channel 1                                                                                                                                                  |

| 13         | AIN0   | Analog input              | Analog input channel 0                                                                                                                                                  |

| 14         | HVDD   | High-voltage power supply | High-voltage positive supply for multiplexer channels                                                                                                                   |

| 15         | HVSS   | High-voltage power supply | High-voltage negative supply for multiplexer channels                                                                                                                   |

| 16         | CS     | Digital input             | Chip select input                                                                                                                                                       |

| 17         | SCLK   | Digital input             | Serial clock input                                                                                                                                                      |

| 18         | DIN    | Digital input             | Serial data input                                                                                                                                                       |

| 19         | DOUT   | Digital output            | Serial data output                                                                                                                                                      |

| 20         | DGND   | Digital power supply      | Digital ground                                                                                                                                                          |

| 21         | DVDD   | Digital power supply      | Digital I/O supply                                                                                                                                                      |

|            |        | Digital output            | Active high, output indicating alarm (programmed as an output pin)                                                                                                      |

| 22         | AL_PD  | Digital input             | Active low, asynchronous power-down (programmed as an input pin, default condition)                                                                                     |

| 23         | REFGND | Analog input              | Reference ground input to device when an external reference is selected.  This pin acts as reference decoupling ground terminal when an internal reference is selected. |

| 24         | REF    | Analog input              | Reference input to device when an external reference is selected.  This pin acts as reference decoupling terminal when an internal reference is selected.               |

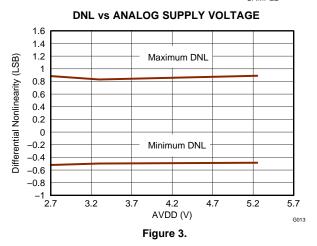

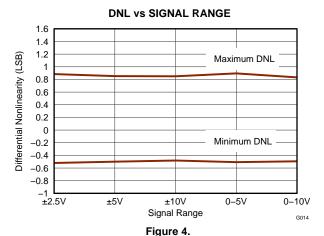

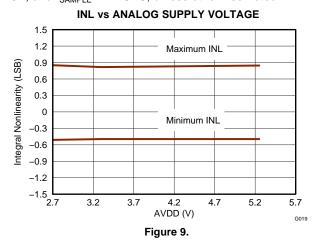

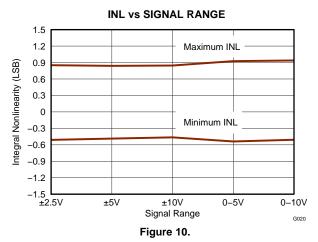

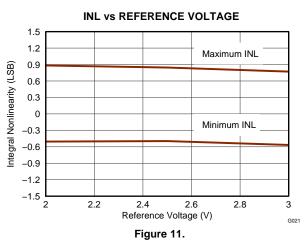

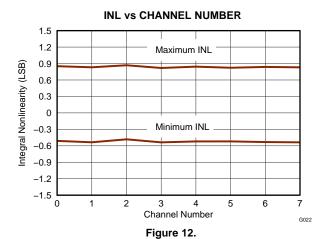

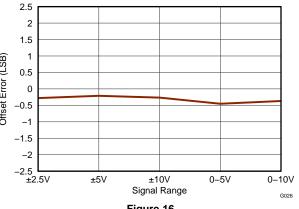

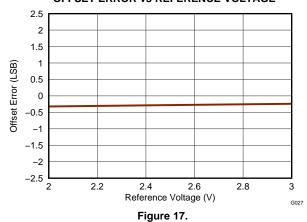

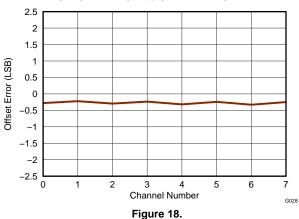

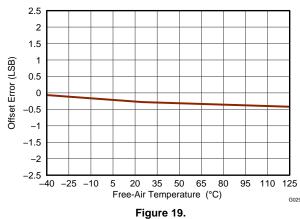

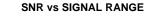

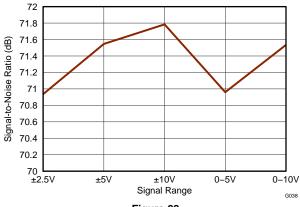

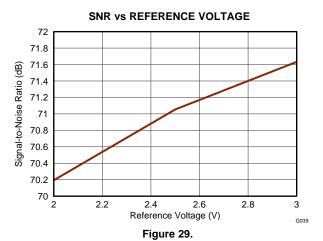

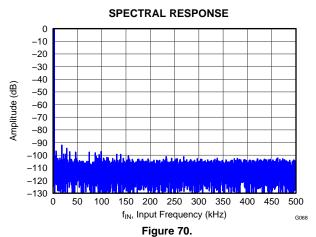

#### TYPICAL CHARACTERISTICS

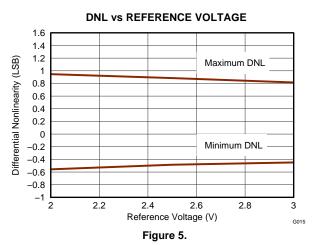

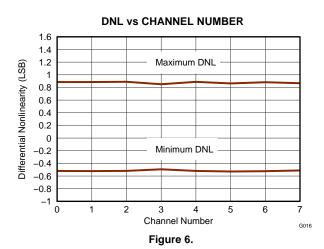

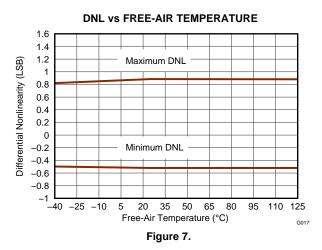

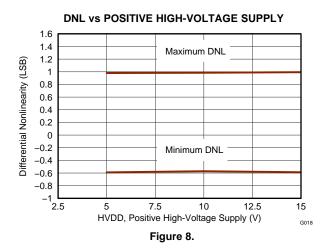

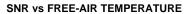

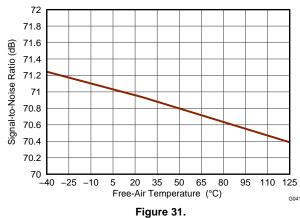

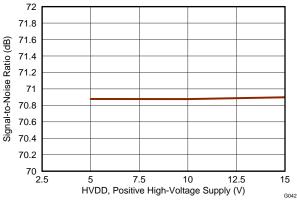

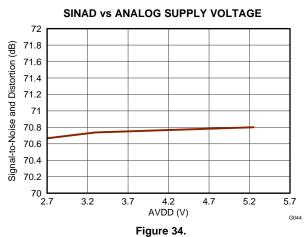

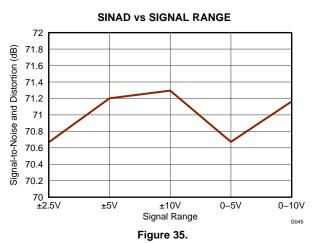

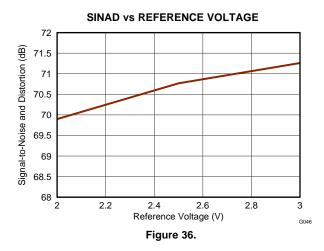

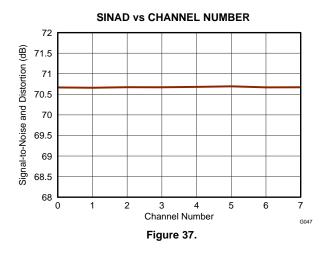

At  $T_A = +25$ °C, internal reference = 2.5V, channel 0, range =  $\pm 2.5$ V, AVDD = 2.7V, DVDD = 1.8V, HVDD = 10V, HVSS = -10V, and  $f_{SAMPLE}$  = 1MSPS, unless otherwise noted.

Figure 16.

#### OFFSET ERROR vs REFERENCE VOLTAGE

Figure 15.

**OFFSET ERROR vs CHANNEL NUMBER**

**OFFSET ERROR vs FREE-AIR TEMPERATURE**

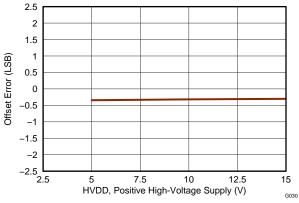

OFFSET ERROR vs POSITIVE HIGH-VOLTAGE SUPPLY

Figure 20.

At  $T_A$  = +25°C, internal reference = 2.5V, channel 0, range = ±2.5V, AVDD = 2.7V, DVDD = 1.8V, HVDD = 10V, HVSS = -10V, and  $f_{SAMPLE}$  = 1MSPS, unless otherwise noted.

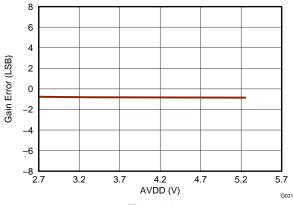

#### **GAIN ERROR vs ANALOG SUPPLY VOLTAGE**

Figure 21.

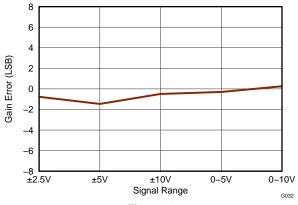

#### **GAIN ERROR vs SIGNAL RANGE**

Figure 22.

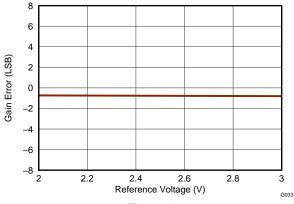

#### **GAIN ERROR vs REFERENCE VOLTAGE**

Figure 23.

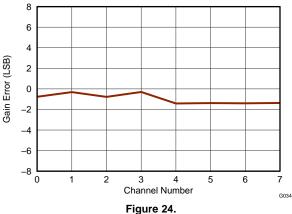

# **GAIN ERROR vs CHANNEL NUMBER**

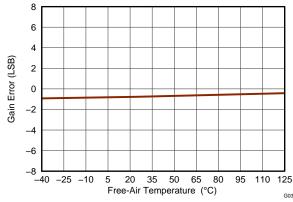

**GAIN ERROR vs FREE-AIR TEMPERATURE**

Figure 25.

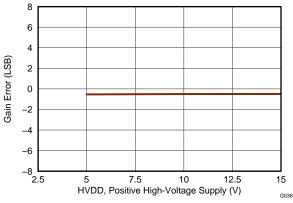

**GAIN ERROR vs POSITIVE HIGH-VOLTAGE SUPPLY**

Figure 26.

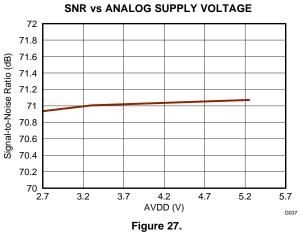

Figure 28.

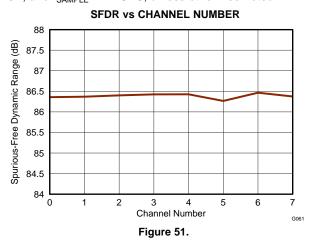

**SNR vs CHANNEL NUMBER**

SNR vs POSITIVE HIGH-VOLTAGE SUPPLY

Figure 32.

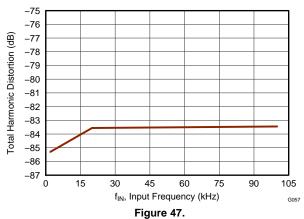

At  $T_A$  = +25°C, internal reference = 2.5V, channel 0, range = ±2.5V, AVDD = 2.7V, DVDD = 1.8V, HVDD = 10V, HVSS = -10V, and  $f_{SAMPLE}$  = 1MSPS, unless otherwise noted.

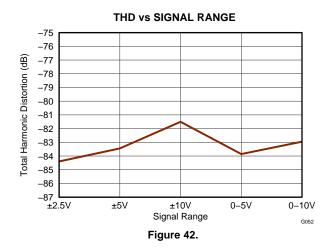

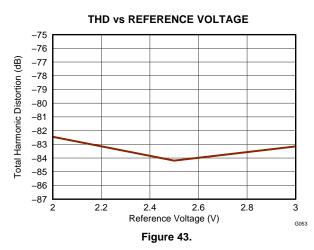

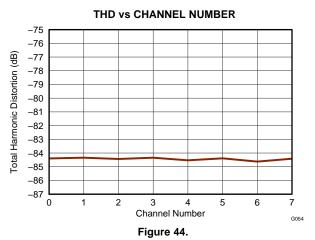

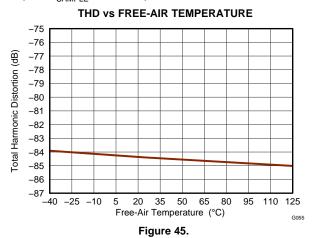

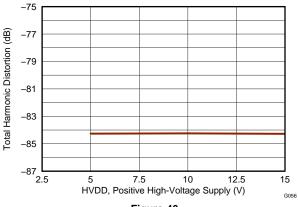

#### THD vs POSITIVE HIGH-VOLTAGE SUPPLY

Figure 46.

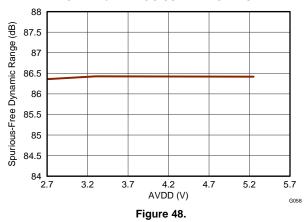

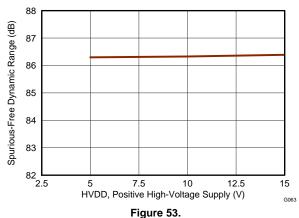

SFDR vs ANALOG SUPPLY VOLTAGE

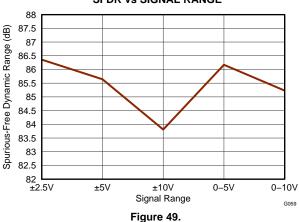

#### SFDR vs SIGNAL RANGE

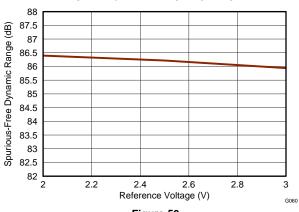

SFDR vs REFERENCE VOLTAGE

Figure 50.

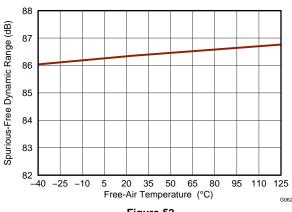

At  $T_A$  = +25°C, internal reference = 2.5V, channel 0, range = ±2.5V, AVDD = 2.7V, DVDD = 1.8V, HVDD = 10V, HVSS = -10V, and  $f_{SAMPLE}$  = 1MSPS, unless otherwise noted.

SFDR vs FREE-AIR TEMPERATURE

Figure 52.

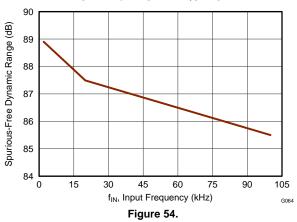

SFDR vs INPUT FREQUENCY

#### **CROSSTALK vs INPUT FREQUENCY**

ANALOG SUPPLY CURRENT (Dynamic) vs ANALOG SUPPLY VOLTAGE

Figure 56.

At  $T_A = +25$ °C, internal reference = 2.5V, channel 0, range =  $\pm 2.5$ V, AVDD = 2.7V, DVDD = 1.8V, HVDD = 10V, HVSS = -10V, and  $f_{SAMPLE}$  = 1MSPS, unless otherwise noted.

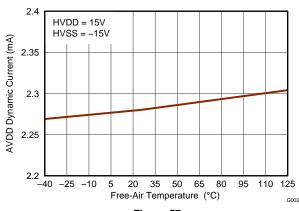

### **ANALOG SUPPLY CURRENT (Dynamic) VS FREE-AIR TEMPERATURE**

Figure 57.

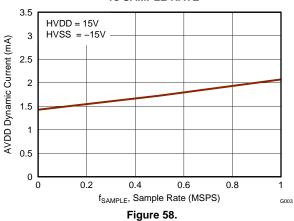

#### **ANALOG SUPPLY CURRENT (Dynamic)** vs SAMPLE RATE

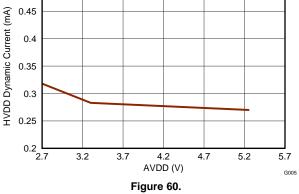

**POSITIVE HIGH-VOLTAGE SUPPLY CURRENT (Dynamic)**

**VS ANALOG SUPPLY VOLTAGE**

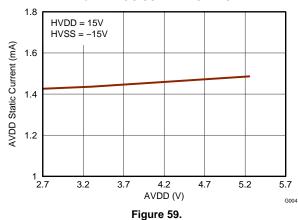

#### **ANALOG SUPPLY CURRENT (Static) vs ANALOG SUPPLY VOLTAGE**

0.35

0.5

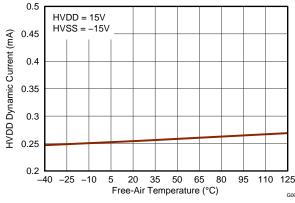

#### **POSITIVE HIGH-VOLTAGE SUPPLY CURRENT (Dynamic)** vs FREE-AIR TEMPERATURE

Figure 61.

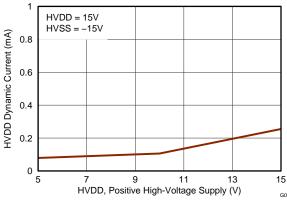

#### **POSITIVE HIGH-VOLTAGE SUPPLY CURRENT (Dynamic) VS POSITIVE HIGH-VOLTAGE SUPPLY**

Figure 62.

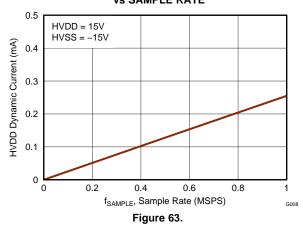

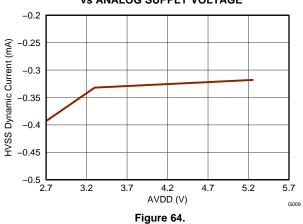

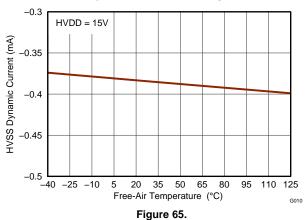

At  $T_A$  = +25°C, internal reference = 2.5V, channel 0, range = ±2.5V, AVDD = 2.7V, DVDD = 1.8V, HVDD = 10V, HVSS = -10V, and  $f_{SAMPLE}$  = 1MSPS, unless otherwise noted.

# POSITIVE HIGH-VOLTAGE SUPPLY CURRENT (Dynamic) vs SAMPLE RATE

# NEGATIVE HIGH-VOLTAGE SUPPLY CURRENT (Dynamic) vs ANALOG SUPPLY VOLTAGE

# NEGATIVE HIGH-VOLTAGE SUPPLY CURRENT (Dynamic) vs FREE-AIR TEMPERATURE

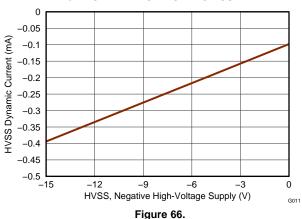

NEGATIVE HIGH-VOLTAGE SUPPLY CURRENT (Dynamic) vs NEGATIVE HIGH-VOLTAGE SUPPLY

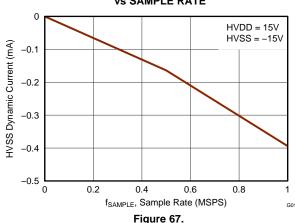

# NEGATIVE HIGH-VOLTAGE SUPPLY CURRENT (Dynamic) vs SAMPLE RATE

#### **OVERVIEW**

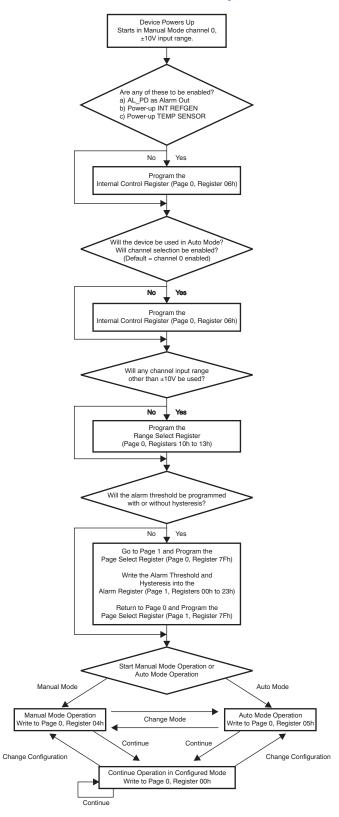

The ADS8634 and ADS8638 are 12-bit, 4- and 8-channel devices, respectively. The ADS8634/8 feature software-selectable bipolar and unipolar ranges, an internal reference with an option to use an external reference, and an internal temperature sensor. Independent power-down control for the internal reference and temperature sensor blocks allows for optimal power based on application. The following sections describe the individual blocks and operation.

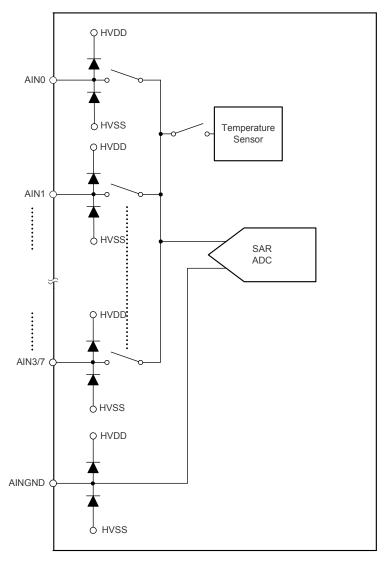

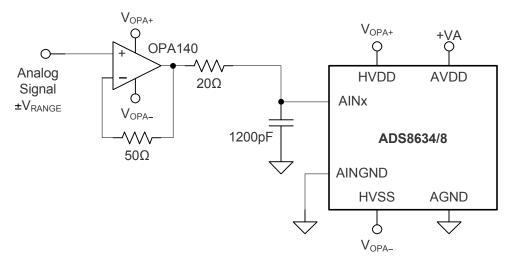

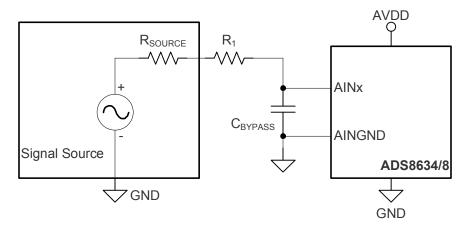

#### **MULTIPLEXER AND ANALOG INPUT**

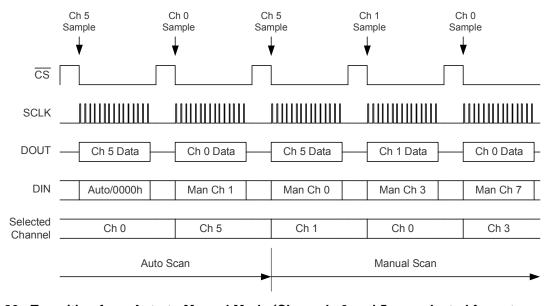

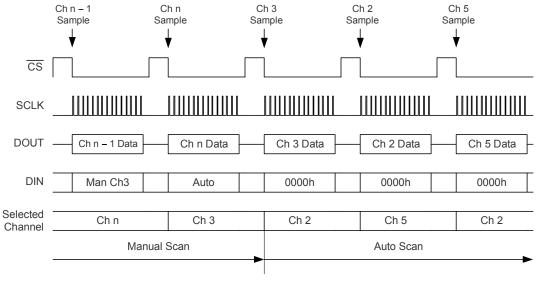

The ADS8634/8 feature single ended inputs with ground sense and a 4-/8-channel, single-pole multiplexer, respectively. The ADC samples the difference voltage between analog input pins *AINx* and the ground sense pin *AINGND*. The ADS8634/8 can scan these analog inputs in either manual or auto-scan mode. In manual mode, the channel is selected for every sample via a register write; in auto-scan mode, the channel number is incremented automatically on every CS falling edge after the present channel is sampled. It is possible to select the analog inputs for an auto scan with register settings. The devices automatically scan only the selected analog inputs in ascending order.

The ADS8634/8 offer multiple software-programmable ranges ±10V, ±5V, ±2.5V, 0V to 5V, and 0V to 10V with a 2.5V reference. Any of these ranges can be assigned to any analog input (for instance, ±10V can be assigned to AIN1, ±2.5V to AIN2, 0V to 10V can be assigned to AIN3, and so on). During a scan (either auto or manual), the programmed signal range is assigned to the selected channel. The range selection, however, can be temporarily overridden using the DIN line for a particular scan. This feature is useful for zooming into a narrow range when needed. Refer to Table 11 for configuration register settings.

Figure 72 shows electrostatic discharge (ESD) diodes connected to the HVDD and HVSS supplies. Make sure these diodes do not turn on by keeping the analog inputs within the specified range.

Figure 72. Analog Inputs

The ADS8634/8 sample the voltage difference ( $V_{AINX} - V_{AINGND}$ ) between the selected analog input channel and the AINGND pin. The ADS8634/8 allow a ±0.2V range on AINGND. This feature is useful in modular systems where the sensor/signal conditioning block is removed from the ADC and when there could be a difference in the ground potential of the sensor/signal condioner from the ADC ground. In such cases, it is recommended to run separate wires from the AINGND terminal of the device to the sensor/signal conditioner ground.

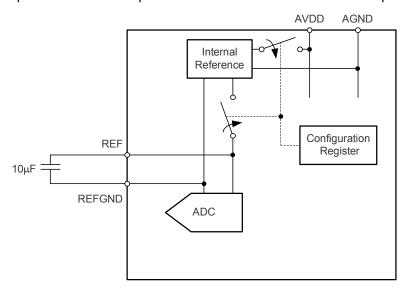

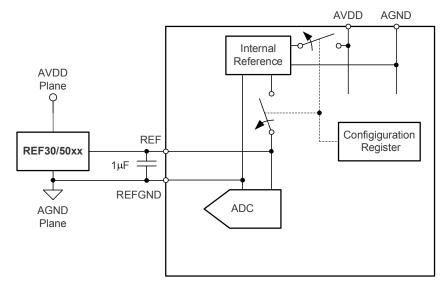

#### REFERENCE

The ADS8634/8 measure the analog input signals relative to the voltage reference using either an internal precision 2.5V voltage reference (Figure 73) or an external voltage reference (Figure 74). Binary-weighted capacitors are switched onto the reference terminal during conversion. The switching frequency is the same as the SCLK frequency. Whether it is an internal or external reference, be sure to decouple the REF terminal to REFGND with a 10µF capacitor. Place the capacitor close to the REFP and REFGND pins.

Figure 73. Operation Using The Internal Reference (Refer to Table 11 for more details on the configuration register settings)

Figure 74. Operation Using an External Reference (Refer to Table 11 for more details on the configiguration register settings)

These devices allow the use of an external reference in the range of 2.0V to 3.0V. The nominal input ranges  $\pm 10V$ ,  $\pm 5V$ ,  $\pm 2.5V$ , 0V to 5V, and 0V to 10V assume a 2.5V reference; a different reference voltage scales the full-scale ranges proportionately. For example, if a 3.0V reference is used and the  $\pm 10V$  range is selected, the actual input range is scaled by (3.0/2.5) for a full-scale range of  $\pm 12V$ .

The internal reference can be enabled/disabled through the configuration register. The reference block is powered down when the internal reference is disabled. Ensure that the internal reference is disabled when the external reference is connected. The external reference is the default selection after power-on or reset.

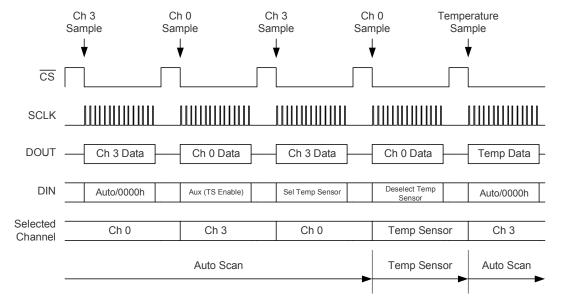

### **TEMPERATURE SENSOR**

The ADS8634/8 feature an on-chip temperature sensoras shown in Figure 75. The device temperature can be read at any time during a scan, either in auto or manual mode. There are three registers associated with the temperature sensor operation. The temperature sensor can be enabled/disabled through the Aux-Config configuration register. Disabling the temperature sensor powers down the temperature block. It is necessary to enable (power up) the temperature sensor at least one cycle before the device temperature sensor is selected with the channel sequencing control registers (manual/auto). This selection overrides the input channel scan sequence and range selection and connects the ADC input to an internal temperature sensor. The temperature sensor must be deselected with channel sequencing control registers (manual/auto) to resume normal scanning. In case of auto-sequencing, the device starts scanning from where it left off before the temperature measurement. The temperature sensor is disabled by default after power-on or reset.

Figure 75. Reading the ADS8634/8 Temperature (Refer to Table 11 for more details on configuration register settings)

The temperature sensor transfer function follows a straight line, as shown in Equation 1:

Output Code =

$$m_{REF}$$

Device Temperature in °C +  $C_{REF}$

(1)

Equation 1 can be re-written as Equation 2:

Device Temperature in  $^{\circ}C$  = (Output Code –  $C_{REF}$ )/ $m_{REF}$

where:

$m_{REF}$  = the slope,

and  $C_{REF}$  = the offset (in ADC output code) of the temperature sensor transfer function (2)

Both  $m_{REF}$  and  $C_{REF}$  change with the reference voltage. The initial values of  $m_{REF}$  and  $C_{REF}$  at a 2.5V reference are:  $m_{REF}$  2.5 = 0.47 and  $C_{REF}$  2.5 = 3777.2

Values of  $m_{REF}$  and  $C_{REF}$  for any reference voltage other than 2.5V can be calculated using Equation 3 and Equation 4:

$$m_{REF} = m_{REF\_2.5} \times 2.5 / V_{REF}$$

(3)

$$C_{REF} = (C_{REF_2.5} - 3584) \times 2.5 / V_{REF} + 3584$$

(4)

For example, at a 2V reference:

$m_{REF\ 2} = 0.47 \times 2.5/2 = 0.59$  and

$C_{REF\ 2} = (3777.2 - 3584) \times 2.5/2 + 3584 = 3825.5$

For the reference voltage used, Equation 2 can be rewritted using  $m_{REF}$  and  $C_{REF}$  as calculated in Equation 3 and Equation 4.

Table 3 can be used as quick reference for temperature sensor transfer function at typical reference values.

Table 3. Temperature Sensor Transfer Function at Typical Reference Values

| REFERENCE VOLTAGE (V) | TRANSFER FUNCTION                                                |

|-----------------------|------------------------------------------------------------------|

| 2                     | Device temperature in °C = (output code – 3825.5)/0.59           |

| 2.5                   | Device temperature in $^{\circ}$ C = (output code – 3777.2)/0.47 |

| 3                     | Device temperature in °C = (output code – 3745.0)/0.39           |

#### **DATA FORMAT**

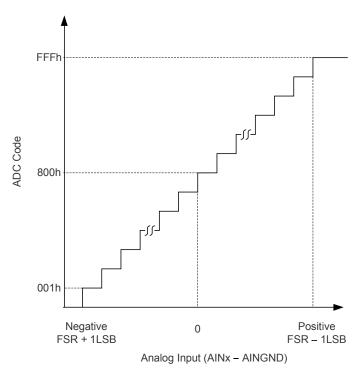

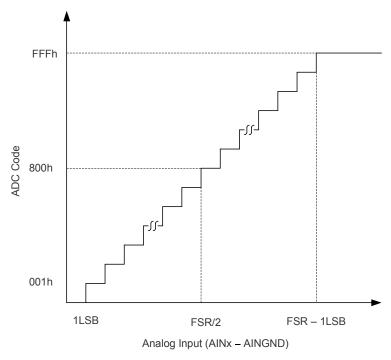

The ADS8634/8 output 12-bits of ADC conversion results in binary format (MSB first) for all ranges, as shown in Table 4. Figure 76 shows the ADC transfer function for bipolar signal ranges. The unipolar range output is shown in Table 5 and Figure 77 shows the transfer function.

Table 4. Bipolar Range Ideal Output Codes<sup>(1)</sup>

|                                                 | INPUT SIGNAL (AINx – AIN                     | IDEAL OUTPUT CODE                      |                   |

|-------------------------------------------------|----------------------------------------------|----------------------------------------|-------------------|

| ±10V RANGE (V)                                  | ±5V RANGE (V)                                | ±2.5V RANGE (V)                        | IDEAL OUTPUT CODE |

| ≥ 10 × (2 <sup>11</sup> - 1)/2 <sup>11(2)</sup> | ≥ 5 × (2 <sup>11</sup> – 1)/2 <sup>11</sup>  | $\geq 2.5 \times (2^{11} - 1)/2^{11}$  | FFFh              |

| 10/2 <sup>11</sup>                              | 5/2 <sup>11</sup>                            | 2.5/2 <sup>11</sup>                    | 801h              |

| 0                                               | 0                                            | 0                                      | 800h              |

| -10 /2 <sup>11</sup>                            | -5/2 <sup>11</sup>                           | -2.5/2 <sup>11</sup>                   | 7FFh              |

| $\leq -10 \times (2^{11} - 1)/2^{11}$           | ≤ -5 × (2 <sup>11</sup> - 1)/2 <sup>11</sup> | $\leq -2.5 \times (2^{11} - 1)/2^{11}$ | 000h              |

<sup>(1)</sup> Excludes noise, offset and gain errors.

Table 5. Unipolar Range Ideal Output Codes (1)

| INPUT SIGNA                          | L (AINx – AINGND)                   |                   |  |  |  |  |  |

|--------------------------------------|-------------------------------------|-------------------|--|--|--|--|--|

| 0V TO 10V RANGE (V)                  | 0V TO 5V RANGE (V)                  | IDEAL OUTPUT CODE |  |  |  |  |  |

| $\geq 10 \times (2^{12} - 1)/2^{12}$ | $\geq 5 \times (2^{12} - 1)/2^{12}$ | FFFh              |  |  |  |  |  |

| 10/2 <sup>12</sup>                   | 5/2 <sup>12</sup>                   | 001h              |  |  |  |  |  |

| < 10/2 <sup>12</sup>                 | < 5/2 <sup>12</sup>                 | 000h              |  |  |  |  |  |

(1) Excludes noise, offset and gain errors.

<sup>(2)</sup> LSB size for the bipolar ranges = positive (or negative) full-scale/2<sup>11</sup>. The ADS8634/8 offer 12-bit resolution across the entire range from positive full-scale to negative full-scale; in other words, the resolution for half range from '0' to positive (or negative) full-scale is 11 bits. For example, a 1LSB for a ±10V range is 10/2<sup>11</sup>.

Figure 76. Transfer Function for Bipolar Signal Ranges

Figure 77. Transfer Function for Unipolar Signal Ranges

#### AL PD: USER-CONFIGURABLE PIN

The ADS8634/8 feature a user-configurable AL\_PD pin. This pin can either be configured as an alarm output (AL) or as a power-down control pin (PD). Refer to the *Page 0, Register Descriptions for the ADS8638* and *Page 0, Register Descriptions for the ADS8634* sections for details.

When programmed as an alarm output, an active-high alarm is flagged on this pin if there is a high or low alarm on any channel. The *Alarm Functionality* section describes the pin details.

When programmed as  $\overline{PD}$ , the AL\_PD pin functions as an active-low power-down input pin. Powering down through this pin is asynchronous. The devices power down immediately after the pin goes low. The *Power-Down Functionality* section describes the pin details.

This pin is configured as a PD input by default after power-on or reset.

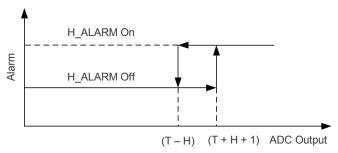

#### **Alarm Functionality**

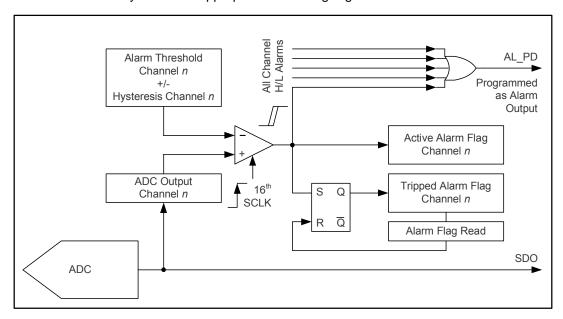

The ADS8634/8 output an active-high alarm on the AL\_PD pin when it is programmed as an AL. AL is synchronous and changes its state on the 16th SCLK rising edge. A high level on AL indicates there is an active alarm on one or more channels. This pin can be wired to interrupt the host input. When an alarm interrupt is received, the alarm flag registers are read to determine which channels have an alarm.

The ADS8634/8 feature independently-programmable alarms for each channel. There are two alarms per channel (low and high alarm) and each alarm threshold has a separate hysteresis setting.

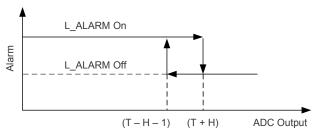

The ADS8634/8 set a high alarm when the digital output for a particular channel exceeds the high alarm upper limit (high alarm threshold T + hysteresis H). The alarm resets when the digital output for the channel is less than or equal to the high alarm lower limit (high alarm T - H). This function is shown in Figure 78.

NOTE: T = alarm threshold and H = hysteresis.

Figure 78. High-Alarm Hysteresis

Similarly, the lower alarm is triggered when the digital output for a particular channel falls below the low alarm lower limit (low alarm threshold T - H). The alarm resets when the digital output for the channel is greater than or equal to the low alarm higher limit (low alarm T + H). This function is shown in Figure 79.

NOTE: T = alarm threshold and H = hysteresis.

Figure 79. Low-Alarm Hysteresis

Figure 80 shows a functional block diagram for a single-channel alarm. For each high and low alarm there are two flags: Active Alarm Flag and Tripped Alarm Flag; refer to the *Alarm Flags for the ADS8638 (Read-Only)* and *Alarm Flags for the ADS8634 (Read-Only)* sections for more details. The active alarm flag is triggered when an alarm condition is encountered for a particular channel; the active alarm flag resets when the alarm shuts off. A tripped alarm flag sets an alarm condition in the same manner as it does for an active alarm flag; however, it remains latched and resets only when the appropriate alarm flag register is read.

Figure 80. Alarm Functionality

#### **Power-Down Functionality**

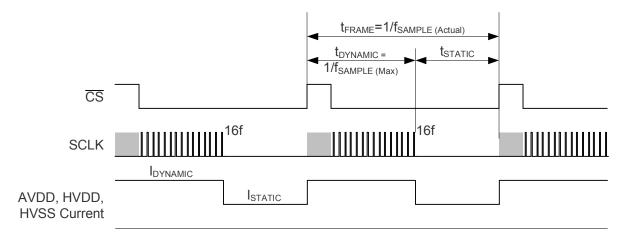

The ADS8634/8 feature a power-down/up control through the programmable AL\_PD pin or the channel sequencing control registers; see the *Channel Sequencing Control Registers for the ADS8638* and *Channel Sequencing Control Registers for the ADS8634* sections for more details. This feature is extremely useful for saving power while running the ADS8634/8 at a slower speed, or for acquiring data at full-speed in bursts and then waiting in a power-down state for the next acquisition start event. Figure 81 through Figure 84 describe entry to and exit from the power-down state.

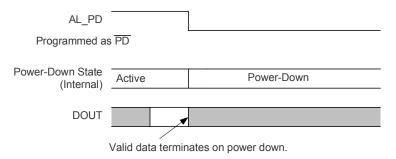

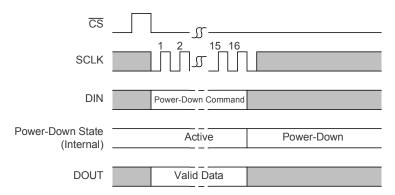

The AL\_PD pin can be programmed as a power-down control pin. The AL\_PD pin, when programmed as  $\overline{PD}$ , is shown in Figure 81. A low on AL\_PD powers down the device immediately; this action is asynchronous operation. Data on DOUT are not valid when the device is in a power-down state.

Figure 81. Power-Down Using the AL\_PD Pin

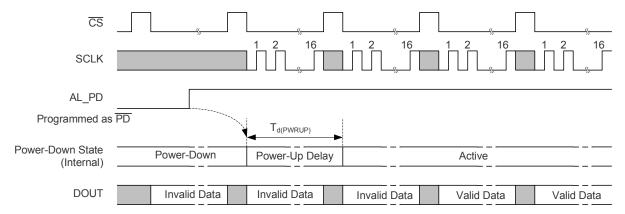

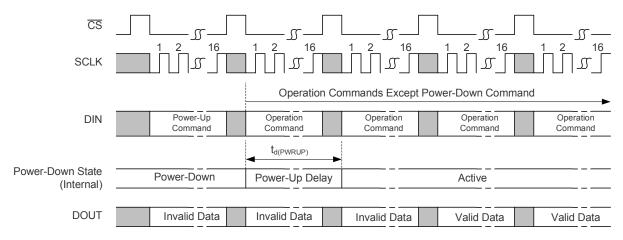

A high level on AL\_PD acts as a power-up request and the power-up sequence begins on the next  $\overline{CS}$  falling edge. The device is active after  $t_{d(PWRUP)}$ . The first valid acquisition initiates in the first data frame (with a  $\overline{CS}$  falling edge) after a power-up delay. The first valid data are presented in the second data frame after the device attains an active state, as shown in Figure 82.

Figure 82. Power-Up Via the AL\_PD Pin

The power-down/up operation can also be controlled with register settings. See the *Channel Sequencing Control Registers for the ADS8638* and *Channel Sequencing Control Registers for the ADS8634* sections for details. Figure 83 illustrates power-down and power-up commands for quick reference.

Figure 83. Power-Down Via Register Write

After receiving a valid power-down command, the device enters a power-down state on 16th SCLK falling edge. An example of this command is given in Table 6.

**Table 6. Power-Down Command Example**

|     | REGISTER ADDRESS     |        |        |        |        |        |       |       |                                               |   |   | DA | TA |          |       |   |

|-----|----------------------|--------|--------|--------|--------|--------|-------|-------|-----------------------------------------------|---|---|----|----|----------|-------|---|

| PIN | Bit 15               | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit |   |   |    |    |          | Bit 0 |   |

| DIN | 0                    | 0      | 0      | 0      | 1      | 0      | X     | 0     | 0                                             | X | X | Χ  | 1  | 1        | 1     | X |

|     | Auto/manual sequence |        |        |        |        |        |       | W     | 0                                             | Х | Х | Χ  | Po | ower-dov | vn    | Х |

The serial interface is active even during a device power-down state. Commands can be issued via the DIN pin during a power-down state.

A power-up command (through DIN) is acknowledged on the next  $\overline{CS}$  falling edge and a power-up sequence initiates. An example of this command is given in Table 7. The device is in an active state after  $t_{d(PWRUP)}$  and initiates a valid acquisition in the first data frame (initiated with a  $\overline{CS}$  falling edge) after a power-up delay. The first valid data are presented in the second data frame after the device attains an active state, as shown in Figure 84.

RD/ **REGISTER ADDRESS** WR DATA Bit 12 Bit 11 PIN Bit 15 Bit 14 Bit 13 Bit 10 Bit 9 Bit 8 Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 Any combination from DIN 0 0 0 Χ 0 0 Х Χ Χ Χ 000 to 110, except 111 W Auto/manual sequence 0 Χ Χ Χ Power-up Χ

**Table 7. Power-Up Command Example**

Figure 84. Power-Up Via Register Write

Use only one method (DIN pin or register settings) for power-down/up control. Do not combine these two methods or the results may be confusing. Do not issue a power-down command through DIN while using the AL\_PD pin. Similarly, do not pull the AL\_PD pin low while using the register write method for power-down/up control.

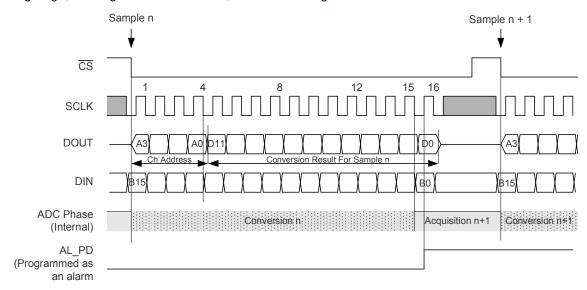

#### DEVICE OPERATION

The ADS8634/8 are 12-bit, 4-/8-channel devices. Each frame begins with a  $\overline{\text{CS}}$  falling edge. The ADS8634/8 sample the input signal from the selected channel on the  $\overline{\text{CS}}$  falling edge and initiate conversion. SCLK is used for conversion and data are output on the DOUT line while conversion is in process. The 16-bit data word contains a 4-bit channel address followed by the 12-bit conversion result in MSB-first format. The MSB of the 4-bit channel address is output on the  $\overline{\text{CS}}$  falling edge; the remaining address bits are clocked out serially for three SCLK falling edges. The MSB of the 12-bit conversion result is output on the fourth SCLK falling edge. Afterwards, the next lower data bits are ouput serially on every subsequen SCLK falling edge. Each data bit can be read (latched) immediately on the next SCLK falling edge from the SCLK falling edge on which the respective data bits are output. For example, if the MSB of a 12-bit data word is output on the fourth SCLK falling edge then the same word can be latched on the fifth SCLK falling edge. Refer to the *Hold time*, *SCLK falling to DOUT valid*, and *Delay time*, *SCLK falling to DOUT* parameters in the *Timing Requirements* section.

The 16-bit word is read on the DIN pin while the data are output on the DOUT pin. DIN data are latched on every SCLK rising edge, starting with the first clock, as shown in Figure 85.

Figure 85. ADS8634/8 Operation

Device configuration and operation mode are controlled through register settings. It is recommended to write to the configuration registers after powering on the device. The configuration information is retained until the devices are powered off or reset. Note that powering down the device with either the AL\_PD pin or a register write does not erase the device configuration.

The ADS8634/8 feature an AL\_PD pin that functions as a alarm output/power-down pin. The pin can be programmed as an alarm output (AL) or it can be programmed as a power-down control pin (PD). When AL\_PD is programmed as an alarm output, it is refreshed on every 16th SCLK rising edge.

#### **CHANNEL SEQUENCING MODES**

The ADS8634/8 offer two channel sequencing modes: auto and manual. In auto-scan mode, the channel number automatically increments every frame. In manual mode, the channel is selected for every frame of a register write. The analog inputs can be selected for an automatic scan with a register setting. The device automatically scans only the selected analog inputs in ascending order.

The auto-mode sequence can be reset at any time during an automatic scan (refer to the *Auto* register in the *PAGE-0 Register Map for the ADS8638* section ). When the reset command has been received, the ongoing auto-mode sequence is reset and restarts it from the lowest selected channel in the sequence.

Figure 86 shows the DIN command sequence for transitions from auto to manual mode. Figure 87 shows the DIN command sequence for transitions from manual to auto-scan mode. Note that each DIN command is executed on the next  $\overline{\text{CS}}$  falling edge.

Figure 86. Transition from Auto to Manual Mode (Channels 0 and 5 are selected for auto sequence)

Figure 87. Transition from Manual to auto-scan mode (Channels 2 and 5 are selected for auto sequence)

#### DEVICE TEMPARATURE READ

The ADS8634/8 feature an internal temperature sensor. The device temperature can be read at any time during any scan. It is essential to enable (power-up) the internal temperature at least one cycle before selecting the temperature sensor for the device temperature measurement. The temperature sensor must be deselected after temperature measurement. The device resumes the channel sequence from where it left the scan after deselection of the temperature sensor. Do not disable (power-down) the temperature sensor before it is deselected. Figure 88 illustrates a typical command sequence for device temperature measurement during an auto scan.

Figure 88. Reading Temperature During Auto Scan (Channels 0 and 3 are selected for auto sequence)

#### **SPI INTERFACE**

The ADS8634/8 employ a four-wire SPI-compatible interface. Apart from the interface,  $\overline{\text{CS}}$  and SCLK also perform an ADC control function.

The data frame is synchronized with the  $\overline{\text{CS}}$  falling edge. A low level on  $\overline{\text{CS}}$  releases the DOUT pin from three-state and the ADC conversion results are output on the DOUT line. Data bits are clocked out on the falling edges of SCLK. The ADS8634/8 sample the analog input signal on the falling edge of  $\overline{\text{CS}}$  and conversion is performed using SCLK.

DOUT is the serial data output line. Depending on register settings, the ADC conversion results are output along with the selected channel address or register data on the DOUT pin. The data output frame always consists of 16 bits. The SDO line goes to three-state after all the 16-bits of data frame are output or after CS goes high.

DIN is a serial data input line. It is used to program various registers for either device configuration or for dynamic changes applicable on the next immediate  $\overline{CS}$  falling edge.

Bits[11:0]

#### **DOUT DATA FORMAT**

The device outputs 16-bit data in every cycle. Table 8 shows the DOUT data format.

#### **Table 8. DOUT Data Format**

|      | CHANNEL ADDRESS |           |           |           |              |        |       |       | CO    | NVERSI | ON RESU | LT    |       |       |       |             |

|------|-----------------|-----------|-----------|-----------|--------------|--------|-------|-------|-------|--------|---------|-------|-------|-------|-------|-------------|

| PIN  | Bit 15          | Bit 14    | Bit 13    | Bit 12    | Bit 11       | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6  | Bit 5   | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0       |

| DOUT | ADDR<br>3       | ADDR<br>2 | ADDR<br>1 | ADDR<br>0 | D11<br>(MSB) | D10    | D9    | D8    | D7    | D6     | D5      | D4    | D3    | D2    | D1    | D0<br>(LSB) |

#### Bit Description for the ADS8638 DOUT Data

#### Bits[15:12] Channel/temperature sensor address

These bits represent the adress of channel or temperature sensor.

0000 = Channel 0 0001 = Channel 1 0010 = Channel 2 0011 = Channel 3 0100 = Channel 4 0101 = Channel 5 0110 = Channel 6 0111 = Channel 7

1111 = Temperature sensor

#### Conversion result for the channel/temperature sensor represented by bits[15:12], in MSB-first format

#### Bit Description for the ADS8634 DOUT Data

#### Bits[15:12] Channel/temperature sensor address

These bits represent the adress of channel or temperature sensor.

000X = Channel 0 001X = Channel 1 010X = Channel 2 011X = Channel 3

1111 = Temperature sensor

## Bits[11:0] Conversion result for the channel/temperature sensor represented by bits[15:12], in MSB-first format

# **DIN DATA FORMAT (SPI COMMAND WORD)**

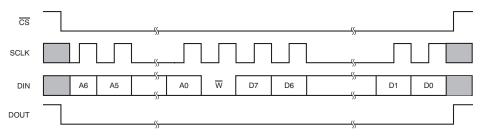

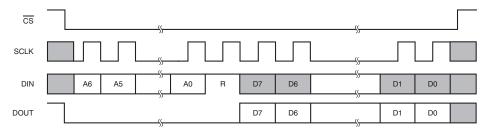

Device registers can be written to and read from. There must be a minimum of 16 SCLKs after the  $\overline{\text{CS}}$  falling edge for any read or write operation. The device receives the command (as shown in Table 9 and Table 10) through DIN where the first seven bits (bits[15:9]) represent the register address and the eighth bit (bit 8) is the read/write instruction. For a write cycle, the next eight bits (bits[7:0]) in the DIN are the desired data for the addressed register (Table 9). For a read cycle, the next eight bits (bits[7:0]) in the DIN are *don't care*. DOUT outputs the 8-bit data from the addressed register (Table 10) during these eight clocks, corresponding to bits[7:0].

**Table 9. Write Cycle Command Word**

|     | REGISTER ADDRESS |           |           |           |           |           |           | RD/<br>WR |       |       |       | DA    | TA    |       |       |       |