Sample &

Buy

#### ADS5400

SLAS611C -OCTOBER 2009-REVISED JANUARY 2016

# ADS5400 12-Bit, 1-GSPS Analog-to-Digital Converter

# 1 Features

- 1-GSPS Sample Rate

- 12-Bit Resolution

- 2.1 GHz Input Bandwidth

- SFDR = 66 dBc at 1.2 GHz

- SNR = 57.6 dBFS at 1.2 GHz

- 7 Clock Cycle Latency

- Interleave Friendly: Internal Adjustments for Gain, Phase, and Offset

- 1.5-V to 2-V Selectable Full-Scale Range

- LVDS-Compatible Outputs, 1 or 2 Bus Options

- Total Power Dissipation: 2.15 W

- On-Chip Analog Buffer

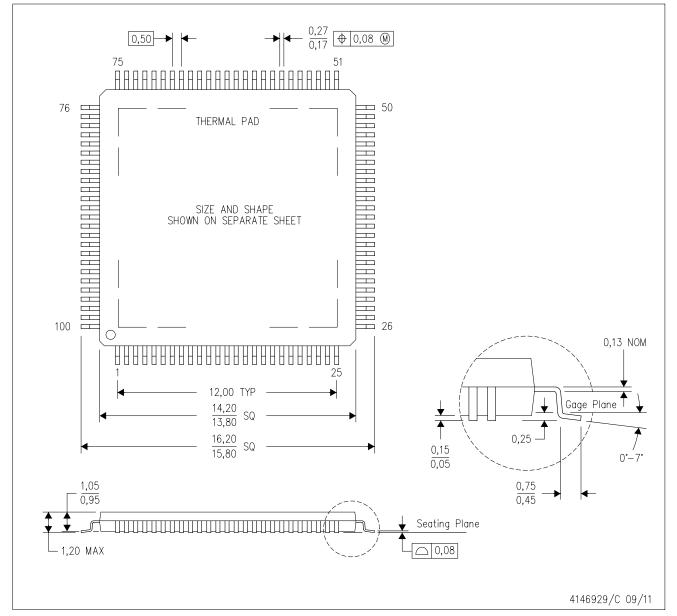

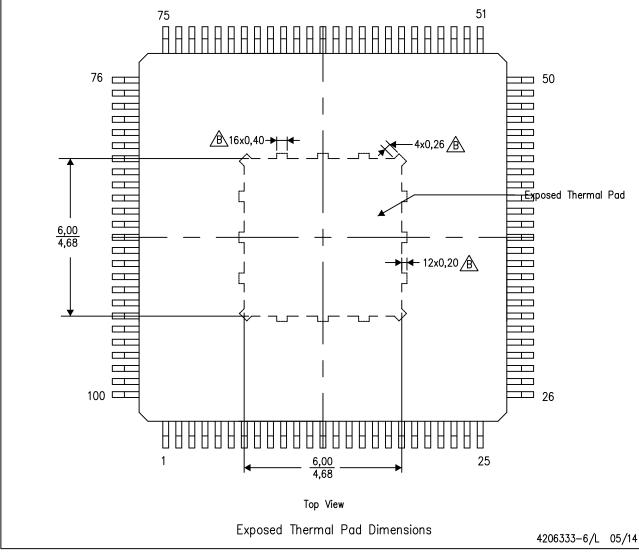

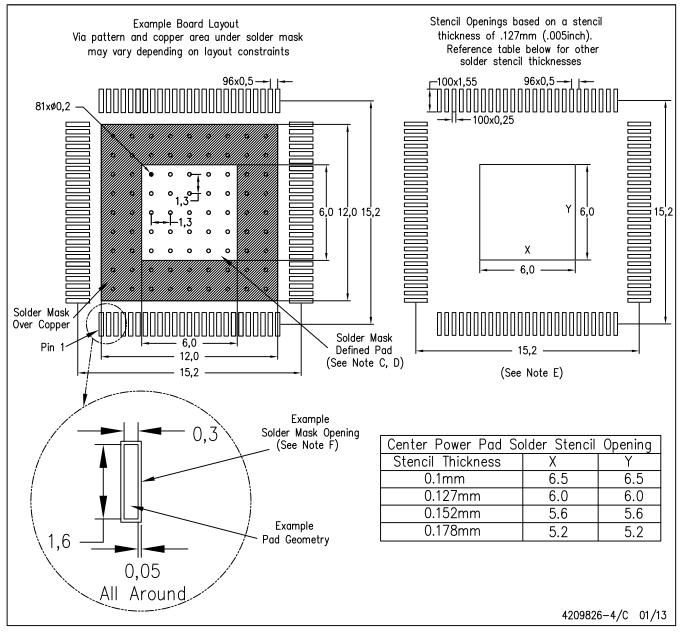

- 100-Pin HTQFP PowerPAD<sup>™</sup> Package (16-mm × 16-mm Footprint With Leads)

- Industrial Temperature Range of –40°C to 85°C

# 2 Applications

- Test and Measurement Instrumentation

- Ultra-Wide Band Software-Defined Radio

- Data Acquisition

- Power Amplifier Linearization

- Signal Intelligence and Jamming

- Radar

# 3 Description

The ADS5400 device is a 12-bit, 1-GSPS analog-todigital converter (ADC) that operates from both a 5-V supply and 3.3-V supply, while providing LVDScompatible digital outputs. The analog input buffer isolates the internal switching of the track and hold from disturbing the signal source. The simple 3-stage pipeline provides extremely low latency for time critical applications. Designed for the conversion of signals up to 2 GHz of input frequency at 1 GSPS, the ADS5400 has outstanding low noise performance and spurious-free dynamic range over a large input frequency range.

The ADS5400 is available in a HTQFP-100 PowerPAD<sup>™</sup> package. The combination of the PowerPAD package and moderate power consumption of the ADS5400 allows for operation without an external heatsink. The ADS5400 is built on Texas Instrument's complementary bipolar process (BiCom3) and is specified over the full industrial temperature range (-40°C to 85°C).

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE     | BODY SIZE (NOM)     |  |  |

|-------------|-------------|---------------------|--|--|

| ADS5400     | HTQFP (100) | 14.00 mm × 14.00 mm |  |  |

(1) For all available packages, see the orderable addendum at the end of the datasheet.

# Table of Contents

| 1 | Features 1     |                                    |  |  |  |

|---|----------------|------------------------------------|--|--|--|

| 2 | Applications 1 |                                    |  |  |  |

| 3 | Des            | cription 1                         |  |  |  |

| 4 | Rev            | ision History 2                    |  |  |  |

| 5 | Pin            | Configuration and Functions 4      |  |  |  |

| 6 | Spe            | cifications                        |  |  |  |

|   | 6.1            | Absolute Maximum Ratings 6         |  |  |  |

|   | 6.2            | ESD Ratings 6                      |  |  |  |

|   | 6.3            | Recommended Operating Conditions 7 |  |  |  |

|   | 6.4            | Thermal Information 7              |  |  |  |

|   | 6.5            | Electrical Characteristics7        |  |  |  |

|   | 6.6            | Interleaving Adjustments9          |  |  |  |

|   | 6.7            | Timing Requirements 10             |  |  |  |

|   | 6.8            | Switching Characteristics 12       |  |  |  |

|   | 6.9            | Typical Characteristics 18         |  |  |  |

| 7 | Deta           | ailed Description 22               |  |  |  |

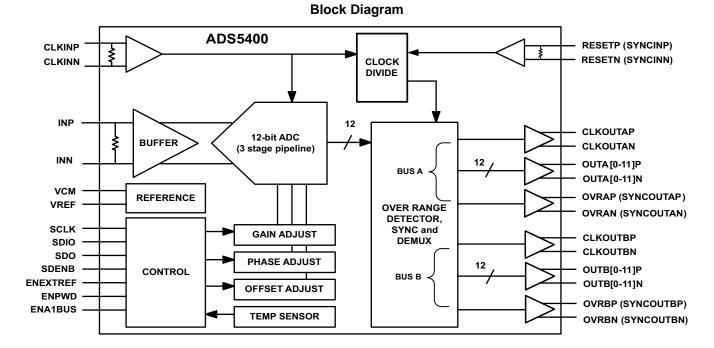

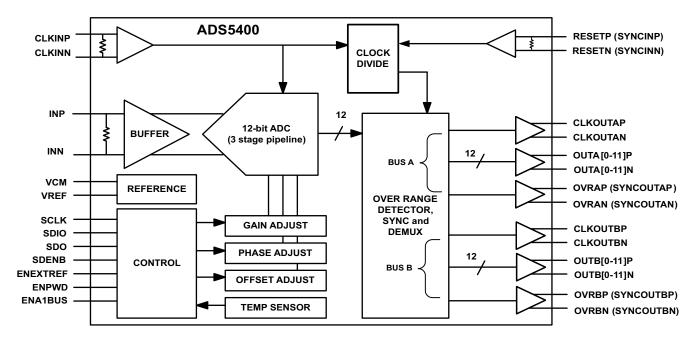

|   | 7.1            | Overview 22                        |  |  |  |

|   | 7.2            | Functional Block Diagram 22        |  |  |  |

|   | 7.3            | Feature Description 22             |  |  |  |

|   |                |                                    |  |  |  |

|    | 7.4  | Device Functional Modes           | 28 |

|----|------|-----------------------------------|----|

|    | 7.5  | Programming                       | 29 |

|    | 7.6  | Register Maps                     |    |

| 8  | App  | lication and Implementation       |    |

|    | 8.1  | Application Information           |    |

|    | 8.2  | Typical Application               | 39 |

| 9  | Pow  | er Supply Recommendations         | 43 |

| 10 | Laye | out                               | 44 |

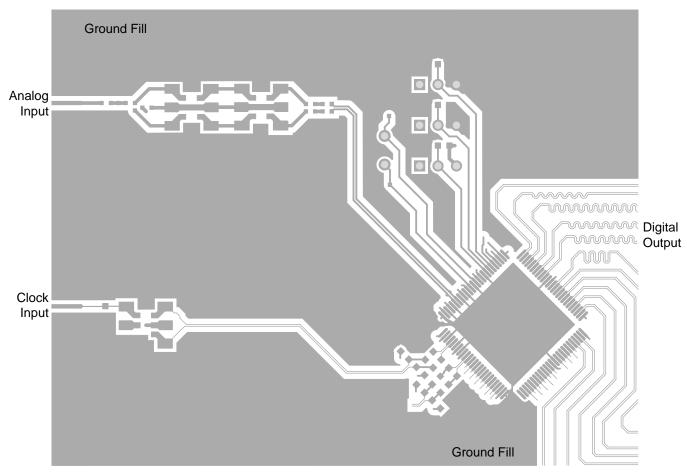

|    | 10.1 | Layout Guidelines                 | 44 |

|    | 10.2 | Layout Example                    | 44 |

|    | 10.3 | PowerPAD <sup>™</sup> Package     | 45 |

| 11 | Dev  | ice and Documentation Support     | 46 |

|    | 11.1 | Device Support                    | 46 |

|    | 11.2 | Documentation Support             | 47 |

|    | 11.3 | Community Resources               | 47 |

|    | 11.4 | Trademarks                        | 47 |

|    | 11.5 | Electrostatic Discharge Caution   | 47 |

|    | 11.6 | Glossary                          | 47 |

| 12 | Mec  | hanical, Packaging, and Orderable |    |

|    |      | mation                            | 47 |

|    |      |                                   |    |

# 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

#### Changes from Revision B (March 2010) to Revision C

| • | Added Pin Configuration and Functions section, ESD Ratings table, Feature Description section, Device Functional |   |

|---|------------------------------------------------------------------------------------------------------------------|---|

|   | Modes, Application and Implementation section, Power Supply Recommendations section, Layout section, Device      |   |

|   | and Documentation Support section, and Mechanical, Packaging, and Orderable Information section                  | 1 |

| • | Deleted Thermal Characteristics table                                                                            | 6 |

#### Changes from Revision A (November 2009) to Revision B

| • | Changed Data sheet From: Product Preview To: Production 1                                                 |

|---|-----------------------------------------------------------------------------------------------------------|

| • | Changed INL - Integral non- linearity error Max value From: 4 To: 4.5                                     |

| • | Changed Worst harmonic/spur (other than HD2 and HD3), f <sub>IN</sub> = 1200 MHz TYP value From: 70 To 66 |

| • | Changed Worst harmonic/spur (other than HD2 and HD3), f <sub>IN</sub> = 1700 MHz TYP value From: 66 To 64 |

| • | Changed Total Harmonic Distortion, f <sub>IN</sub> = 125 MHz TYP value From: 73.5 To 71.7                 |

| • | Changed Total Harmonic Distortion, f <sub>IN</sub> = 600 MHz TYP value From: 68.5 To 67                   |

| • | Changed Total Harmonic Distortion, f <sub>IN</sub> = 850 MHz TYP value From: 68.5 To 66.5                 |

| • | Changed Total Harmonic Distortion, f <sub>IN</sub> = 1700 MHz TYP value From: 56.2 To 55.7                |

| • | Changed Signal-to-noise and distortion, $f_{IN}$ = 125 MHz TYP value From: 58 To 58.5                     |

| • | Changed Signal-to-noise and distortion, $f_{IN}$ = 600 MHz TYP value From: 57.4 To 58.2                   |

| • | Changed Signal-to-noise and distortion, $f_{IN}$ = 850 MHz TYP value From: 57.3 To 57.8                   |

| • | Changed Signal-to-noise and distortion, $f_{IN}$ = 1200 MHz TYP value From: 57.2 To 57.5                  |

| • | Changed Signal-to-noise and distortion, $f_{IN}$ = 1700 MHz TYP value From: 54 To 54.2                    |

| • | Changed Effective number of bits (using SINAD in dBFS), $f_{IN}$ = 125 MHz TYP value From: 9.34 To 9.42   |

| • | Changed Effective number of bits (using SINAD in dBFS), $f_{IN}$ = 600 MHz TYP value From: 9.24 To 9.37   |

| • | Changed Effective number of bits (using SINAD in dBFS), $f_{IN}$ = 850 MHz TYP value From: 9.23 To 9.3    |

| • | Changed INPUT CLOCK COARSE PHASE ADJUSTMENT, Integral Non-Linearity error Max value From: 4 To 5 10       |

www.ti.com

•

Page

Page

2

|                  | Submit Documentation Feedback |

|------------------|-------------------------------|

| 1.1.1.4.0.05.400 |                               |

# SLAS611C-OCTOBER 2009-REVISED JANUARY 2016

ADS5400

| C | hanges from Original (October 2009) to Revision A                                                                                                                                                       | Page |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| • | Changed the FEATURES list                                                                                                                                                                               | 1    |

| • | Deleted text "Internal pull-down resistor" from the SCLK, SDIO, and SDO pins in the Pin Functions table                                                                                                 | 5    |

| • | Changed the SDENB pin text From: "Internal pull-up resistor" To: "Internal 100kΩ pull-up resisto" in the Pin Functions table                                                                            | 5    |

| • | Added Note to the Pin Functions table - This pin contains an internal ~40kΩ pull-down resistor, to ground                                                                                               |      |

| • | Changed Abs Max, Recommended Op Conditions, and Electrical Specs values.                                                                                                                                |      |

| • | Changed the description of the ANALOG INPUT entry in the Rec Op Condition table From: Differential input range To: Full-scale differential input range                                                  |      |

| • | Changed the Rec Op table, V <sub>CM</sub> - TYP value From: 2.5V To AVDD5/2                                                                                                                             | 7    |

| • | Changed the description of the ANALOG INPUT entry in the Elect Char table From: Differential input range To: Full-<br>scale differential input range                                                    |      |

| • | Changed the Elect Char table, V <sub>CM</sub> - TYP value From: 2.5V To AVDD5/2                                                                                                                         | 7    |

| • | Changed the Timing Diagrams illustrations                                                                                                                                                               | 13   |

| • | Changed Figure 1                                                                                                                                                                                        | 13   |

| • | Changed Figure 2                                                                                                                                                                                        | 14   |

| • | Changed Figure 3                                                                                                                                                                                        | 15   |

| • | Changed Figure 4                                                                                                                                                                                        | 16   |

| • | Changed Figure 5                                                                                                                                                                                        | 17   |

| • | Changed the TYPICAL CHARACTERISTICS, Conditions Note From: DVDD3 = $3.3 \text{ V}$ , and $3.3 \text{ V}_{PP}$ differential clock To: DVDD = $3.3 \text{ V}$ and $1.5 \text{ V}_{PP}$ differential clock |      |

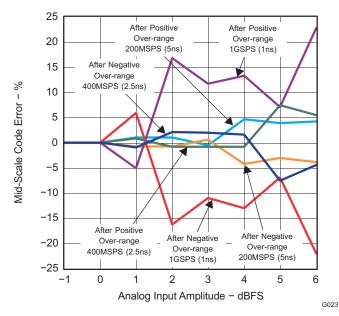

| • | Added subsection - Analog Input Over-Range Recovery Error                                                                                                                                               | 24   |

| • | Changed the Clock Inputs subsection                                                                                                                                                                     | 24   |

| • | Changed the Test Patterns subsection                                                                                                                                                                    | 27   |

| • | Changed the Interleaving subsection                                                                                                                                                                     | 28   |

| • | Changed Table 6 BIT <7:3>, Title and description                                                                                                                                                        | 33   |

| • | Changed Table 7 BIT <0>, Default setting description, and BIT <7:2> description                                                                                                                         | 33   |

| • | Changed Table 8 BIT <0>, Default setting description                                                                                                                                                    | 34   |

| • | Changed Serial Register 0x06 (Read or Write) (Table 10). Bits 4 and 5 From TBD To: 0                                                                                                                    | 36   |

| • | Deleted Table 10 description comment from BIT <7:6> 11: (this mode is not working properly on early samples - will be fixed)                                                                            |      |

| • | Changed the Power Supplies subsection                                                                                                                                                                   | 43   |

| • | Added Figure 40 - Was TBD                                                                                                                                                                               | 43   |

www.ti.com

3

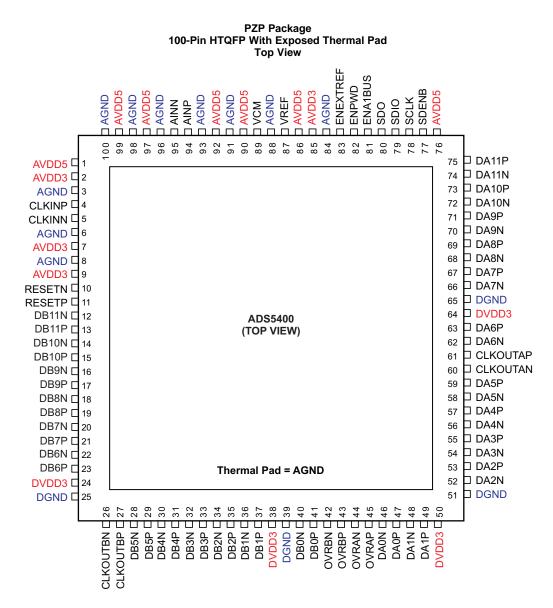

# 5 Pin Configuration and Functions

# **Pin Functions**

| PIN TURE                                         |                           |              |                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|--------------------------------------------------|---------------------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NO.                                              | NAME                      | TYPE         | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                         |  |

| 3, 6, 8,<br>84, 88,<br>91, 93,<br>96, 98,<br>100 | AGND                      | Ground       | Analog ground                                                                                                                                                                                                                                                                                                                                                                                       |  |

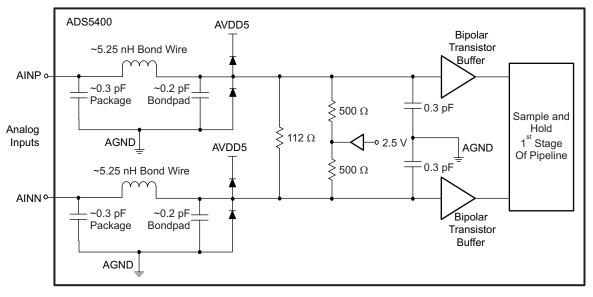

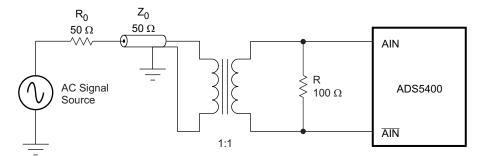

| 94, 95                                           | AINP, AINN                | Input        | Analog differential input signal (positive, negative). Includes 100- $\Omega$ differential load on-chip.                                                                                                                                                                                                                                                                                            |  |

| 2, 7, 9,<br>85                                   | AVDD3                     | Supply       | Analog power supply (3.3 V)                                                                                                                                                                                                                                                                                                                                                                         |  |

| 1, 76, 86,<br>90, 92,<br>97, 99                  | AVDD5                     | Supply       | Analog power supply (5 V)                                                                                                                                                                                                                                                                                                                                                                           |  |

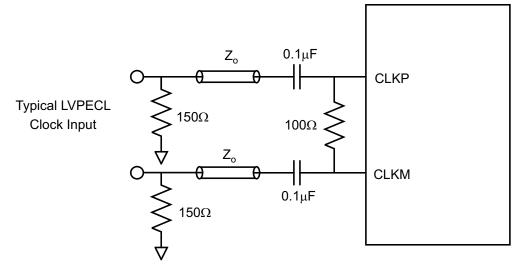

| 4, 5                                             | CLKINP, CLKINN            | Input        | Differential input clock (positive, negative). Includes 160-Ω differential load on-chip.                                                                                                                                                                                                                                                                                                            |  |

| 60, 61                                           | CLKOUTAN,<br>CLKOUTAP     | Output       | Bus A, Clock output (Data ready), LVDS output pair                                                                                                                                                                                                                                                                                                                                                  |  |

| 26, 27                                           | CLKOUTBN,<br>CLKOUTBP     | Output       | Bus B, Clock output (Data ready), LVDS output pair                                                                                                                                                                                                                                                                                                                                                  |  |

| 46, 47                                           | DA0N, DA0P                | Output       | Bus A, LVDS digital output pair, least-significant bit (LSB) (P = positive output, N = negative output)                                                                                                                                                                                                                                                                                             |  |

| 48-49,<br>52-59,<br>62-63,<br>66-73              | DA1N–DA10N,<br>DA1P-DA10P | Output       | Bus A, LVDS digital output pairs (bits 1- 10)                                                                                                                                                                                                                                                                                                                                                       |  |

| 74, 75                                           | DA11N, DA11P              | Output       | Bus A, LVDS digital output pair, most-significant bit (MSB)                                                                                                                                                                                                                                                                                                                                         |  |

| 40, 41                                           | DB0N, DB0P                | Output       | Bus B, LVDS digital output pair, least-significant bit (LSB) (P = positive output, N = negative output)                                                                                                                                                                                                                                                                                             |  |

| 14-23,<br>28-37                                  | DB1N–DB10N,<br>DB1P-DB10P | Output       | Bus B, LVDS digital output pairs (bits 1- 10)                                                                                                                                                                                                                                                                                                                                                       |  |

| 12, 13                                           | DB11N, DB11P              | Output       | Bus B, LVDS digital output pair, most-significant bit (MSB)                                                                                                                                                                                                                                                                                                                                         |  |

| 25, 39,<br>51, 65                                | DGND                      | Ground       | Digital ground                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 24, 38,<br>50, 64                                | DVDD3                     | Supply       | Output driver power supply (3.3 V)                                                                                                                                                                                                                                                                                                                                                                  |  |

| 81 <sup>(1)</sup>                                | ENA1BUS                   | Input        | Enable single output bus mode (2-bus mode is default), active high. This pin is logic OR'd with addr 0x02h bit<0>.                                                                                                                                                                                                                                                                                  |  |

| 83 <sup>(1)</sup>                                | ENEXTREF                  | Input        | Enable External Reference Mode, active high. Device uses an external voltage reference when high. This pin is logic OR'd with addr 0x05h bit<2>.                                                                                                                                                                                                                                                    |  |

| 82 <sup>(1)</sup>                                | ENPWD                     | Input        | Enable Powerdown, active high. Places the converter into power-saving sleep mode when high. This pin is logic OR'd with addr 0x05h bit<6>.                                                                                                                                                                                                                                                          |  |

| 44, 45                                           | OVRAN, OVRAP              | Output       | Bus A, Overrange indicator LVDS output. A logic high signals an analog input in excess of the full-scale range. Becomes SYNCOUTA when SYNC mode is enabled in register 0x05.                                                                                                                                                                                                                        |  |

| 42, 43                                           | OVRBN, OVRBP              | Output       | Bus B, Overrange indicator LVDS output. A logic high signals an analog input in excess of the full-scale range. Becomes SYNCOUTB when SYNC mode is enabled in register 0x05.                                                                                                                                                                                                                        |  |

| 10, 11                                           | RESETN,<br>RESETP         | Input        | Digital Reset Input, LVDS input pair. Inactive if logic low. When clocked in a high state, this is used for resetting the polarity of CLKOUT signal pair(s). If SYNC mode is enabled in register 0x05, this input also provides a SYNC time-stamp with the data sample present when RESET is clocked by the ADC, as well as CLKOUT polarity reset. Includes $100-\Omega$ differential load on-chip. |  |

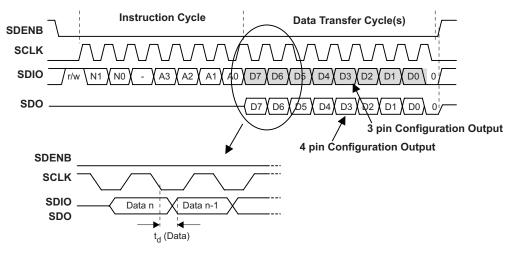

| 78                                               | SCLK                      | Input        | Serial interface clock.                                                                                                                                                                                                                                                                                                                                                                             |  |

| 77                                               | SDENB                     | Input        | Active low serial data enable, always an input. Use to enable the serial interface. Internal $100 \text{k}\Omega$ pull-up resistor.                                                                                                                                                                                                                                                                 |  |

| 79                                               | SDIO                      | Input/Output | Bidirectional serial interface data in 3-pin mode (default) for programming/reading internal registers. In 4-pin interface mode (reg 0x01), the SDIO pin is an input only.                                                                                                                                                                                                                          |  |

(1) This pin contains an internal ~40k $\Omega$  pull-down resistor, to ground.

#### TEXAS INSTRUMENTS

www.ti.com

# **Pin Functions (continued)**

| PIN |      | TYPE                                                                                                                                                                | DESCRIPTION                                                                                                                                                 |  |  |

|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NO. | NAME | TIPE                                                                                                                                                                | DESCRIPTION                                                                                                                                                 |  |  |

| 80  | SDO  | Output Unidirectional serial interface data in 4-pin mode (reg 0x01) provides internal settings. The SDO pin is in high-impedance state in 3-pin interface mode (de |                                                                                                                                                             |  |  |

| 89  | VCM  | Input/Output                                                                                                                                                        | Analog input common mode voltage, Output (for DC-coupled applications, nominally 2.5 V). A 0.1- $\mu$ F capacitor to AGND is recommended, but not required. |  |  |

|     |      | Input                                                                                                                                                               | Reference voltage input (2 V nominal). A 0.1- $\mu$ F capacitor to AGND is recommended, but not required.                                                   |  |  |

# 6 Specifications

# 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|             |                                                   |                                                               |                      | MIN           | MAX              | UNIT |

|-------------|---------------------------------------------------|---------------------------------------------------------------|----------------------|---------------|------------------|------|

|             | AVDD5 to GND                                      |                                                               |                      |               | 6                | V    |

|             | AVDD3 to GND                                      |                                                               |                      |               | 5                | V    |

|             | DVDD3 to GND                                      |                                                               |                      |               | 5                | V    |

| Supply      | AINP, AINN to GND <sup>(2)</sup>                  | Voltage difference between pin and ground                     |                      | 0.5           | 4.5              | V    |

| voltage     |                                                   | Voltage difference                                            | Short duration       | -0.3          | (AVDD5 + 0.3)    | V    |

|             | AINP to AINN <sup>(2)</sup>                       | between pins, common mode at AVDD5/2                          | Continuous AC signal | 1.25          | 3.75             | V    |

|             |                                                   |                                                               | Continuous DC signal | 1.75          | 3.25             | V    |

|             | CLKINP, CLKINN to GND <sup>(2)</sup>              | Voltage difference between pin and ground                     |                      | 0.5           | 4.5              | V    |

|             | CLKINP to CLKINN <sup>(2)</sup>                   | Voltage difference<br>between pins, common<br>mode at AVDD5/2 | Continuous AC signal | 1.1           | 3.9              | V    |

|             |                                                   |                                                               | Continuous DC signal | 2             | 3                | V    |

|             | RESETP, RESETN to GND <sup>(2)</sup>              | Voltage difference between pin and ground                     |                      | -0.3          | (AVDD5 + 0.3)    | V    |

| Din voltogo | RESETP to RESETN <sup>(2)</sup>                   | Voltage difference between pins                               | Continuous AC signal | 1.1           | 3.9              | V    |

| Pin voltage |                                                   |                                                               | Continuous DC signal | 2             | 3                | V    |

|             | Data/OVR Outputs to GND <sup>(2)</sup>            |                                                               |                      |               | (DVDD3 +<br>0.3) | V    |

|             | SDENB, SDIO, SCLK to GND <sup>(2)</sup>           | Voltage difference between pin and ground                     |                      | -0.3          | (AVDD3 + 0.3)    |      |

|             | ENA1BUS, ENPWD,<br>ENEXTREF to GND <sup>(2)</sup> |                                                               | -0.3                 | (AVDD5 + 0.3) |                  |      |

|             | Operating                                         |                                                               |                      | -40           | 85               | °C   |

| Temperature | Maximum junction , T <sub>J</sub>                 |                                                               |                      |               | 150              | °C   |

|             | Storage, T <sub>stg</sub>                         |                                                               |                      | -65           | 150              | °C   |

(1) Stresses above these ratings may cause permanent damage. Exposure to absolute maximum conditions for extended periods may degrade device reliability. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those specified is not implied. Kirkendall voidings and current density information for calculation of expected lifetime is available upon request.

(2) Valid when supplies are within recommended operating range.

# 6.2 ESD Ratings

|                    |  |                                                                                | VALUE | UNIT |

|--------------------|--|--------------------------------------------------------------------------------|-------|------|

| V <sub>(ESD)</sub> |  | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | 2000  | V    |

|                    |  | Charged device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | 500   | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 6.3 Recommended Operating Conditions

|                 |                                     | MIN   | NOM     | MAX   | UNIT            |

|-----------------|-------------------------------------|-------|---------|-------|-----------------|

| SUPPL           | IES                                 |       |         |       |                 |

|                 | Analog supply voltage, AVDD5        | 4.75  | 5       | 5.25  | V               |

|                 | Analog supply voltage, AVDD3        | 3.135 | 3.3     | 3.465 | V               |

|                 | Digital supply voltage, DVDD3       | 3.135 | 3.3     | 3.465 | V               |

| ANALC           | DG INPUT                            |       |         |       |                 |

|                 | Full-scale differential input range | 1.52  |         | 2     | V <sub>PP</sub> |

| V <sub>CM</sub> | Input common mode                   |       | AVDD5/2 |       | V               |

| DIGITA          | L OUTPUT                            |       |         |       |                 |

|                 | Differential output load            |       |         | 5     | pF              |

| CLOCK           | ( INPUT                             |       |         |       |                 |

|                 | CLK input sample rate (sine wave)   | 100   |         | 1000  | MSPS            |

|                 | Clock amplitude, differential       | 0.6   |         | 1.5   | V <sub>PP</sub> |

|                 | Clock duty cycle                    | 45%   | 50%     | 55%   |                 |

| T <sub>A</sub>  | Open free-air temperature           | -40   |         | 85    | °C              |

# 6.4 Thermal Information

|                       |                                              | ADS5400     |      |

|-----------------------|----------------------------------------------|-------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | PZP (HTQFP) | UNIT |

|                       |                                              | 100 PINS    |      |

| $R_{	extsf{	heta}JA}$ | Junction-to-ambient thermal resistance       | 34.5        | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 7.4         | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 9.1         | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 0.2         | °C/W |

| Ψ <sub>JB</sub>       | Junction-to-board characterization parameter | 9           | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 0.4         | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

# 6.5 Electrical Characteristics

Typical values at  $T_A = 25^{\circ}$ C, minimum and maximum values over full temperature range  $T_{MIN} = -40^{\circ}$ C to  $T_{MAX} = 85^{\circ}$ C, sampling rate = 1 GSPS, 50% clock duty cycle, AVDD5 = 5 V, AVDD3 = 3.3 V, DVDD3 = 3.3 V, -1-dBFS differential input, and 1.5 V<sub>PP</sub> differential clock (unless otherwise noted)

|                  | PARAMETER                           | TEST CONDITIONS                                                   | MIN  | ТҮР    | MAX | UNIT            |

|------------------|-------------------------------------|-------------------------------------------------------------------|------|--------|-----|-----------------|

| ANALOO           | G INPUTS                            | · · ·                                                             |      |        |     |                 |

|                  | Full-scale differential input range | Programmable                                                      | 1.52 |        | 2   | V <sub>PP</sub> |

| V <sub>CM</sub>  | Common-mode input                   | Self-biased to AVDD5 / 2                                          | А    | VDD5/2 |     | V               |

| R <sub>IN</sub>  | Input resistance, differential (DC) |                                                                   | 85   | 100    | 115 | Ω               |

| C <sub>IN</sub>  | Input capacitance                   | Estimated to ground from each AIN pin, excluding soldered package |      | 0.8    |     | pF              |

| CMRR             | Common-mode rejection ratio         | Common mode signal = 125 MHz                                      | 40   |        |     | dB              |

| INTERN           | AL REFERENCE VOLTAGE                |                                                                   |      |        |     |                 |

| V <sub>REF</sub> | Reference voltage                   |                                                                   |      | 2      |     | V               |

| DYNAMI           | C ACCURACY                          |                                                                   |      |        |     |                 |

|                  | Resolution                          | No missing codes                                                  | 12   |        |     | Bits            |

| DNL              | Differential linearity error        | f <sub>IN</sub> = 125 MHz                                         | -1   | ±0.7   | 2   | LSB             |

| INL              | Integral non- linearity error       | f <sub>IN</sub> = 125 MHz                                         | -4   | ±2     | 4.5 | LSB             |

|                  | Offset error                        | default is trimmed near 0 mV                                      | -2.5 | 0      | 2.5 | mV              |

|                  | Offset temperature coefficient      |                                                                   |      | 0.02   |     | mV /°C          |

Copyright © 2009–2016, Texas Instruments Incorporated

SLAS611C - OCTOBER 2009-REVISED JANUARY 2016

www.ti.com

# **Electrical Characteristics (continued)**

Typical values at  $T_A = 25^{\circ}$ C, minimum and maximum values over full temperature range  $T_{MIN} = -40^{\circ}$ C to  $T_{MAX} = 85^{\circ}$ C, sampling rate = 1 GSPS, 50% clock duty cycle, AVDD5 = 5 V, AVDD3 = 3.3 V, DVDD3 = 3.3 V, -1-dBFS differential input, and 1.5 V<sub>PP</sub> differential clock (unless otherwise noted)

|                      | PARAMETER                                            | TEST CONDITIONS                                                       | MIN  | TYP  | MAX  | UNIT                |

|----------------------|------------------------------------------------------|-----------------------------------------------------------------------|------|------|------|---------------------|

|                      | Gain error                                           |                                                                       | -5   |      | 5    | % full scale        |

|                      | Gain temperature coefficient                         |                                                                       |      | 0.03 |      | % full scale<br>/°C |

| POWER                | SUPPLY <sup>(1)</sup>                                | ·                                                                     |      |      |      |                     |

| 1                    | 5-V analog supply current (Bus A and B active)       | $f_{IN} = 125 \text{ MHz},$<br>$f_S = 1 \text{ GSPS}$                 |      | 220  | 234  | mA                  |

| I <sub>(AVDD5)</sub> | 5-V analog supply current (Bus A active)             | $f_{IN} = 125 \text{ MHz},$<br>$f_S = 1 \text{ GSPS}$                 |      | 225  | 241  | mA                  |

|                      | 3.3-V analog supply current (Bus A and B active)     | f <sub>IN</sub> = 125 MHz,<br>f <sub>S</sub> = 1 GSPS                 |      | 219  | 234  | mA                  |

| I <sub>(AVDD3)</sub> | 3.3-V analog supply current (Bus A active)           | f <sub>IN</sub> = 125 MHz,<br>f <sub>S</sub> = 1 GSPS                 |      | 226  | 242  | mA                  |

| I <sub>(DVDD3)</sub> | 3.3-V digital supply current<br>(Bus A and B active) | $f_{IN} = 125 \text{ MHz},$<br>$f_S = 1 \text{ GSPS}$                 |      | 136  | 154  | mA                  |

| .(00003)             | 3.3-V digital supply current (Bus A active)          | $f_{IN} = 125 \text{ MHz},$<br>$f_S = 1 \text{ GSPS}$                 |      | 71   | 81   | mA                  |

|                      | Total power dissipation<br>(BUS A and B active)      | $f_{IN} = 125 \text{ MHz},$<br>$f_S = 1 \text{ GSPS}$                 |      | 2.28 | 2.45 | W                   |

|                      | Total power dissipation<br>(Bus A active)            | $f_{IN} = 125 \text{ MHz},$<br>$f_S = 1 \text{ GSPS}$                 |      | 2.15 | 2.25 | W                   |

|                      | Total power dissipation                              | ENPWD = logic High (sleep enabled)                                    |      | 13   | 50   | mW                  |

|                      | Wake-up time from sleep                              |                                                                       |      | 1.8  |      | ms                  |

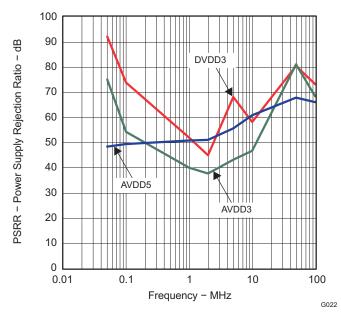

| PSRR                 | Power-supply rejection ratio                         | 1MHz injected to each supply,<br>measured without external decoupling |      | 50   |      | dB                  |

| DYNAMI               | C AC CHARACTERISTICS                                 |                                                                       |      |      |      |                     |

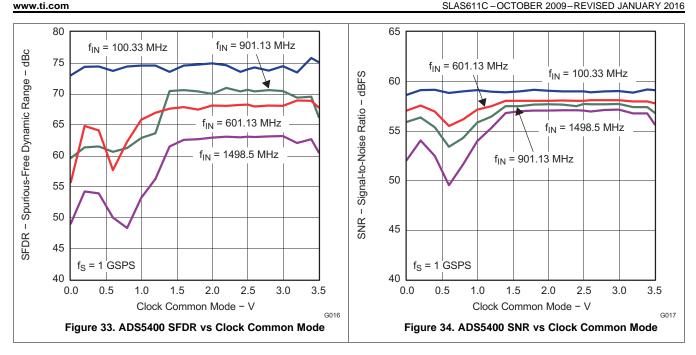

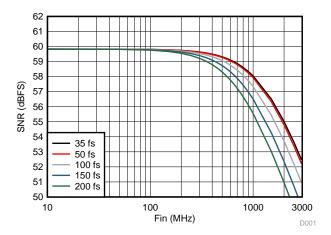

|                      |                                                      | f <sub>IN</sub> = 125 MHz                                             | 57   | 58.5 |      |                     |

|                      |                                                      | f <sub>IN</sub> = 600 MHz                                             | 56.5 | 58.2 |      |                     |

| SNR                  | Signal-to-noise ratio                                | f <sub>IN</sub> = 850 MHz                                             | 56   | 57.8 |      | dBFS                |

|                      |                                                      | f <sub>IN</sub> = 1200 MHz                                            |      | 57.6 |      |                     |

|                      |                                                      | f <sub>IN</sub> = 1700 MHz                                            |      | 55.7 |      |                     |

|                      |                                                      | f <sub>IN</sub> = 125 MHz                                             | 65   | 75   |      |                     |

|                      |                                                      | f <sub>IN</sub> = 600 MHz                                             | 63   | 72   |      |                     |

| SFDR                 | Spurious-free dynamic range                          | f <sub>IN</sub> = 850 MHz                                             | 60   | 71   |      | dBc                 |

|                      |                                                      | f <sub>IN</sub> = 1200 MHz                                            |      | 66   |      |                     |

|                      |                                                      | f <sub>IN</sub> = 1700 MHz                                            |      | 56   |      |                     |

|                      |                                                      | f <sub>IN</sub> = 125 MHz                                             | 65   | 78   |      |                     |

|                      |                                                      | f <sub>IN</sub> = 600 MHz                                             | 63   | 78   |      |                     |

| HD2                  | Second harmonic                                      | f <sub>IN</sub> = 850 MHz                                             | 60   | 71   |      | dBc                 |

|                      |                                                      | f <sub>IN</sub> = 1200 MHz                                            |      | 66   |      |                     |

|                      |                                                      | f <sub>IN</sub> = 1700 MHz                                            |      | 56   |      |                     |

|                      |                                                      | f <sub>IN</sub> = 125 MHz                                             | 65   | 80   |      |                     |

|                      |                                                      | f <sub>IN</sub> = 600 MHz                                             | 63   | 72   |      |                     |

| HD3                  | Third harmonic                                       | f <sub>IN</sub> = 850 MHz                                             | 60   | 72   |      | dBc                 |

|                      |                                                      | f <sub>IN</sub> = 1200 MHz                                            |      | 70   |      |                     |

|                      |                                                      | f <sub>IN</sub> = 1700 MHz                                            |      | 65   |      |                     |

(1) All power values assume LVDS output current is set to 3.5 mA.

#### **Electrical Characteristics (continued)**

Typical values at  $T_A = 25^{\circ}$ C, minimum and maximum values over full temperature range  $T_{MIN} = -40^{\circ}$ C to  $T_{MAX} = 85^{\circ}$ C, sampling rate = 1 GSPS, 50% clock duty cycle, AVDD5 = 5 V, AVDD3 = 3.3 V, DVDD3 = 3.3 V, -1-dBFS differential input, and 1.5 V<sub>PP</sub> differential clock (unless otherwise noted)

| PARAMETER                          | TEST CONDITIONS                                                                                                        | MIN  | TYP  | MAX | UNIT    |

|------------------------------------|------------------------------------------------------------------------------------------------------------------------|------|------|-----|---------|

|                                    | f <sub>IN</sub> = 125 MHz                                                                                              | 65   | 80   |     |         |

|                                    | f <sub>IN</sub> = 600 MHz                                                                                              | 63   | 72   |     |         |

|                                    | f <sub>IN</sub> = 850 MHz                                                                                              | 60   | 72   |     | dBc     |

|                                    | f <sub>IN</sub> = 1200 MHz                                                                                             |      | 66   |     |         |

|                                    | f <sub>IN</sub> = 1700 MHz                                                                                             |      | 64   |     |         |

|                                    | f <sub>IN</sub> = 125 MHz                                                                                              | 63   | 71.7 |     |         |

|                                    | f <sub>IN</sub> = 600 MHz                                                                                              | 62   | 67   |     |         |

| HD Total Harmonic Distortion       | f <sub>IN</sub> = 850 MHz                                                                                              | 59   | 66.5 |     | dBc     |

|                                    | f <sub>IN</sub> = 1200 MHz                                                                                             |      | 65.1 |     |         |

|                                    | f <sub>IN</sub> = 1700 MHz                                                                                             |      | 55.7 |     |         |

|                                    | f <sub>IN</sub> = 125 MHz                                                                                              | 56   | 58.5 |     |         |

|                                    | f <sub>IN</sub> = 600 MHz                                                                                              | 55   | 58.2 |     |         |

| NAD Signal-to-noise and distortion | f <sub>IN</sub> = 850 MHz                                                                                              | 54   | 57.8 |     | dBFS    |

|                                    | f <sub>IN</sub> = 1200 MHz                                                                                             |      | 57.5 |     |         |

|                                    | f <sub>IN</sub> = 1700 MHz                                                                                             |      | 54.2 |     |         |

|                                    | $f_{IN1}$ = 247.5 MHz, $f_{IN2}$ = 252.5 MHz,<br>each tone at –7 dBFS                                                  |      | 74.6 |     |         |

| T / 0500                           | $f_{IN1}$ = 247.5 MHz, $f_{IN2}$ = 252.5 MHz,<br>each tone at -11 dBFS                                                 |      | 80.4 |     | 1050    |

| Two-tone SFDR                      | $f_{IN1}$ = 1197.5 MHz, $f_{IN2}$ = 1202.5 MHz, each tone at -7 dBFS                                                   |      | 70   |     | dBFS    |

|                                    | $f_{IN1} = 1197.5 \text{ MHz}, f_{IN2} = 1202.5 \text{ MHz},$<br>each tone at -11 dBFS                                 |      | 78.3 |     |         |

|                                    | f <sub>IN</sub> = 125 MHz                                                                                              | 9    | 9.42 |     |         |

| Effective number of bits (using    | f <sub>IN</sub> = 600 MHz                                                                                              | 8.84 | 9.37 |     | Bits    |

|                                    | f <sub>IN</sub> = 850 MHz                                                                                              | 8.67 | 9.3  |     |         |

| DMO tills also and a size          | lands the data second and the                                                                                          |      | 1.41 |     | LSB rms |

| KIVIS IGIE-Channel noise           | inputs tied to common-mode                                                                                             |      | 60.2 |     | dBFS    |

| _                                  | Worst harmonic/spur (other than HD2<br>and HD3) Total Harmonic Distortion Signal-to-noise and distortion Two-tone SFDR |      |      |     |         |

#### 6.6 Interleaving Adjustments

Typical values at  $T_A = 25^{\circ}$ C, Minimum and maximum values over full temperature range  $T_{MIN} = -40^{\circ}$ C to  $T_{MAX} = 85^{\circ}$ C, sampling rate = 1 GSPS, 50% clock duty cycle, AVDD5 = 5 V, AVDD3 = 3.3 V, DVDD3 = 3.3 V, and 1.5 V<sub>PP</sub> differential clock (unless otherwise noted)

|        | PARAMETER                         | TEST CONDITIONS                                       | MIN  | TYP | MAX | UNIT |

|--------|-----------------------------------|-------------------------------------------------------|------|-----|-----|------|

| OFFSE  | T ADJUSTMENTS                     |                                                       |      |     |     |      |

|        | Resolution                        |                                                       | 9    |     |     | Bits |

|        | LSB magnitude                     | At full scale range of 2 V <sub>PP</sub>              |      | 120 |     | μV   |

| DNL    | Differential linearity error      |                                                       | -2.5 |     | 2.5 | LSB  |

| INL    | Integral Non-Linearity error      |                                                       | -3   |     | 3   | LSB  |

|        | Recommended Min Offset<br>Setting | From default offset value, to maintain AC performance |      | -8  |     | mV   |

|        | Recommended Max Offset<br>Setting | From default offset value, to maintain AC performance |      | 8   |     | mV   |

| GAIN A | DJUSTMENTS                        |                                                       |      |     |     |      |

|        | Resolution                        |                                                       | 12   |     |     | Bits |

|        | LSB magnitude                     |                                                       |      | 120 |     | μV   |

SLAS611C - OCTOBER 2009-REVISED JANUARY 2016

www.ti.com

#### Interleaving Adjustments (continued)

Typical values at  $T_A = 25^{\circ}$ C, Minimum and maximum values over full temperature range  $T_{MIN} = -40^{\circ}$ C to  $T_{MAX} = 85^{\circ}$ C, sampling rate = 1 GSPS, 50% clock duty cycle, AVDD5 = 5 V, AVDD3 = 3.3 V, DVDD3 = 3.3 V, and 1.5 V<sub>PP</sub> differential clock (unless otherwise noted)

|       | PARAMETER                     | TEST CONDITIONS | MIN  | TYP    | MAX | UNIT            |

|-------|-------------------------------|-----------------|------|--------|-----|-----------------|

| DNL   | Differential linearity error  |                 | -4   | -2, +1 | 4   | LSB             |

| INL   | Integral Non-Linearity error  |                 | -8   | -2, +4 | 8   | LSB             |

|       | Min Gain Setting              |                 |      | 1.52   |     | V <sub>PP</sub> |

|       | Max Gain Setting              |                 |      | 2      |     | V <sub>PP</sub> |

| INPUT | CLOCK FINE PHASE ADJUSTMENT   | -               | 1    |        | i.  |                 |

|       | Resolution                    |                 | 6    |        |     | Bits            |

|       | LSB magnitude                 |                 |      | 116    |     | fs              |

| DNL   | Differential linearity error  |                 | -2   |        | 2.5 | LSB             |

| INL   | Integral Non-Linearity error  |                 | -2.5 |        | 4   | LBS             |

|       | Max Fine Clock Skew setting   |                 |      | 7.4    |     | ps              |

| INPUT | CLOCK COARSE PHASE ADJUSTN    | IENT            |      |        |     |                 |

|       | Resolution                    |                 | 5    |        |     | Bits            |

|       | LSB magnitude                 |                 |      | 2.4    |     | ps              |

| DNL   | Differential linearity error  |                 | -1   |        | 1   | LSB             |

| INL   | Integral Non-Linearity error  |                 | -1   |        | 5   | LSB             |

|       | Max Coarse Clock Skew setting |                 |      | 73     |     | ps              |

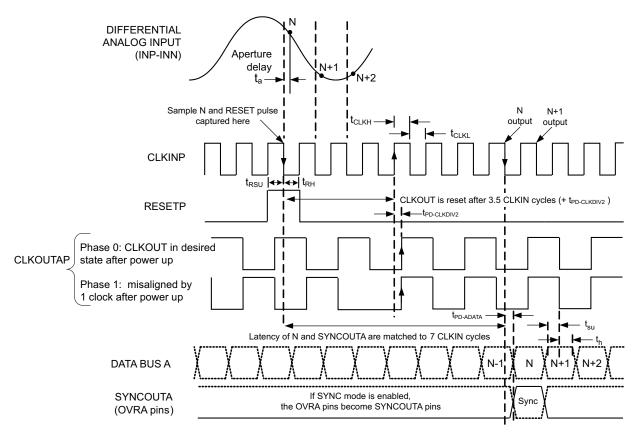

# 6.7 Timing Requirements

Typical values at  $T_A = 25^{\circ}$ C, Minimum and maximum values over full temperature range  $T_{MIN} = -40^{\circ}$ C to  $T_{MAX} = 85^{\circ}$ C, sampling rate = 1 GSPS, 50% clock duty cycle, AVDD5 = 5 V, AVDD3 = 3.3 V, DVDD3 = 3.3 V, and 1.5 V<sub>PP</sub> differential clock (unless otherwise noted)<sup>(1)</sup>.

|                                    |                              |                                                            | MIN  | NOM                             | MAX  | UNIT   |

|------------------------------------|------------------------------|------------------------------------------------------------|------|---------------------------------|------|--------|

| ta                                 | Aperture delay               |                                                            |      | 250                             |      | ps     |

|                                    | Aperture jitter, rms         | Uncertainty of sample point due to internal jitter sources |      | 125                             |      | fs     |

|                                    |                              | Bus A, using Single Bus Mode                               |      | 7                               |      |        |

|                                    | Latanay                      | Bus A, using Dual Bus Mode Aligned                         |      | 7.5                             |      | Cualaa |

|                                    | Latency                      | Bus B, using Dual Bus Mode Aligned                         |      | 8.5                             |      | Cycles |

|                                    |                              | Bus A and B, using Dual Bus Mode Staggered                 |      | 7.5                             |      |        |

| LVDS OUTPU                         | UT TIMING (DATA, CLKOUT, O   | /R/SYNCOUT) <sup>(2)</sup>                                 |      |                                 |      |        |

| t <sub>CLK</sub>                   | Clock period                 |                                                            | 1    |                                 | 10   | ns     |

| t <sub>CLKH</sub>                  | Clock pulse duration, high   | Assuming worst case 45/55 duty cycle                       | 0.45 |                                 |      | ns     |

| t <sub>CLKL</sub>                  | Clock pulse duration, low    | Assuming worst case 55/45 duty cycle                       | 0.45 |                                 |      | ns     |

| t <sub>PD-CLKDIV2</sub>            | Clock propagation delay      | CLKIN rising to CLKOUT rising in divide by 2 mode          | 700  | 1200                            | 1700 | ps     |

| t <sub>PD-CLKDIV4</sub>            | Clock propagation delay      | CLKIN rising to CLKOUT rising in divide by 4 mode          | 700  | 1200                            | 1700 | ps     |

| t <sub>PD-ADATA</sub>              | Bus A data propagation delay | CLKIN falling to Data Output transition                    | 700  | 1400                            | 2100 | ps     |

| t <sub>PD-BDATA</sub>              | Bus B data propagation delay | CLKIN falling to Data Output transition                    | 700  | 1400                            | 2100 | ps     |

| t <sub>SU-SBM</sub> <sup>(3)</sup> | Setup time, single bus mode  | Data valid to CLKOUT edge, 50% CLKIN duty cycle            | 290p | (t <sub>CLK</sub> /2) -<br>185p |      | s      |

(1) Timing parameters are specified by design or characterization, but not production tested.

(2) LVDS output timing measured with a differential 100-Ω load placed ~4 inches from the ADS5400. Measured differential load capacitance is 3.5 pF. Measurement probes and other parasitics add ~1 pF. Total approximate capacitive load is 4.5 pF differential. All timing parameters are relative to the device pins, with the loading as stated.

(3) In single bus mode at 1 GSPS (1-ns clock), the minimum output setup/hold times over process and temperature provide a minimum 700 ps of data valid window, with 300 ps of uncertainity.

# **Timing Requirements (continued)**

Typical values at  $T_A = 25^{\circ}$ C, Minimum and maximum values over full temperature range  $T_{MIN} = -40^{\circ}$ C to  $T_{MAX} = 85^{\circ}$ C, sampling rate = 1 GSPS, 50% clock duty cycle, AVDD5 = 5 V, AVDD3 = 3.3 V, DVDD3 = 3.3 V, and 1.5 V<sub>PP</sub> differential clock (unless otherwise noted)<sup>(1)</sup>.

|                      |                            |                                                             | MIN   | NOM                            | MAX | UNIT |

|----------------------|----------------------------|-------------------------------------------------------------|-------|--------------------------------|-----|------|

| t <sub>H-SBM</sub>   | Hold time, single bus mode | CLKOUT edge to Data invalid, 50% CLKIN duty cycle           | 410p  | (t <sub>CLK</sub> /2) -<br>65p |     | S    |

| t <sub>SU-DBM</sub>  | Setup time, dual bus mode  | Data valid to CLKOUT edge, 50% CLKIN duty cycle             | 550p  | t <sub>СLК</sub> -<br>425р     |     | S    |

| t <sub>H-DBM</sub>   | Hold time, dual bus mode   | CLKOUT edge to Data invalid, 50% CLKIN duty cycle           | 1150p | t <sub>CLK</sub> +<br>175p     |     | s    |

| t <sub>r</sub>       | LVDS rise time             | Measured 20% to 80%                                         |       | 400                            |     | ps   |

| t <sub>f</sub>       | LVDS output fall time      | Measured 20% to 80%                                         |       | 400                            |     | ps   |

| LVDS INPU            | T TIMING (RESETIN)         |                                                             |       |                                |     |      |

| t <sub>RSU</sub>     | RESET setup time           | RESETP going HIGH to CLKINP going LOW                       | 300   |                                |     | ps   |

| t <sub>RH</sub>      | RESET hold time            | CLKINP going LOW to RESETP going LOW                        | 300   |                                |     | ps   |

|                      | RESET input capacitance    | Differential                                                |       | 1                              |     | pF   |

|                      | RESET input current        |                                                             |       | ±1                             |     | μA   |

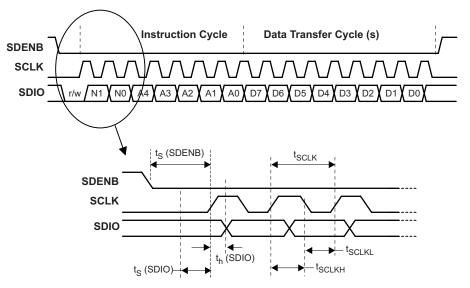

| SERIAL INT           | ERFACE TIMING              |                                                             |       |                                |     |      |

| t <sub>S-SDENB</sub> | Setup time, serial enable  | SDENB falling to SCLK rising                                | 20    |                                |     | ns   |

| t <sub>H-SDENB</sub> | Hold time, serial enable   | SCLK falling to SENDB rising                                | 25    |                                |     | ns   |

| t <sub>S-SDIO</sub>  | Setup time, SDIO           | SDIO valid to SCLK rising                                   | 10    |                                |     | ns   |

| t <sub>H-SDIO</sub>  | Hold time, SDIO            | SCLK rising to SDIO transition                              | 10    |                                |     | ns   |

| f <sub>SCLK</sub>    | Frequency                  |                                                             |       |                                | 10  | MHz  |

| t <sub>SCLK</sub>    | SCLK period                |                                                             | 100   |                                |     | ns   |

| t <sub>SCLKH</sub>   | Minimum SCLK high time     |                                                             | 40    |                                |     | ns   |

| t <sub>SCLKL</sub>   | Minimum SCLK low time      |                                                             | 40    |                                |     | ns   |

| t <sub>r</sub>       | Rise time                  | 10 pF                                                       |       | 10                             |     | ns   |

| t <sub>f</sub>       | Fall time                  | 10 pF                                                       |       | 10                             |     | ns   |

| t <sub>DDATA</sub>   | Data output delay          | Data output (SDO/SDIO) delay after SCLK falling, 10-pF load | 75    |                                |     | ns   |

#### ADS5400

SLAS611C - OCTOBER 2009-REVISED JANUARY 2016

www.ti.com

# 6.8 Switching Characteristics

Typical values at  $T_A = 25^{\circ}$ C, Minimum and maximum values over full temperature range  $T_{MIN} = -40^{\circ}$ C to  $T_{MAX} = 85^{\circ}$ C, sampling rate = 1 GSPS, 50% clock duty cycle, AVDD5 = 5 V, AVDD3 = 3.3 V, DVDD3 = 3.3 V, and 1.5 V<sub>PP</sub> differential clock (unless otherwise noted)

|                 | PARAMETER                       | TEST CONDITIONS                                                            | MIN   | TYP  | MAX         | UNIT |

|-----------------|---------------------------------|----------------------------------------------------------------------------|-------|------|-------------|------|

| LVDS D          | IGITAL OUTPUTS (DATA, OVR/SYN   | COUT, CLKOUT)                                                              |       |      |             |      |

| V <sub>OD</sub> | Differential output voltage (±) | Terminated 100 Ω differential                                              | 247   | 350  | 454         | mV   |

| V <sub>OC</sub> | Common mode output voltage      | Terminated 100 Ω differential                                              | 1.125 | 1.25 | 1.375       | V    |

| LVDS D          | IGITAL INPUTS (RESET)           |                                                                            |       |      |             |      |

| V <sub>ID</sub> | Differential input voltage (±)  | Each input pin                                                             | 175   | 350  |             | mV   |

| V <sub>IC</sub> | Common mode input voltage       | Each input pin                                                             | 0.1   | 1.25 | 2.4         | V    |

| R <sub>IN</sub> | Input resistance                |                                                                            | 85    | 100  | 115         | Ω    |

| CIN             | Input capacitance               | Each pin to ground                                                         |       | 0.6  |             | pF   |

| DIGITAL         | INPUTS (SCLK, SDIO, SDENB)      |                                                                            |       |      |             |      |

| V <sub>IH</sub> | High level input voltage        |                                                                            | 2     |      | AVDD3 + 0.3 | V    |

| V <sub>IL</sub> | Low level input voltage         |                                                                            | 0     |      | 0.8         | V    |

| IIH             | High level input current        |                                                                            |       | ±1   |             | μA   |

| IIL             | Low level input current         |                                                                            |       | ±1   |             | μA   |

| C <sub>IN</sub> | Input capacitance               |                                                                            |       | 2    |             | pF   |

| DIGITAL         | INPUTS (ENEXTREF, ENPWD, EN     | A1BUS)                                                                     |       |      |             |      |

| VIH             | High level input voltage        |                                                                            | 2     |      | AVDD5 + 0.3 | V    |

| VIL             | Low level input voltage         |                                                                            | 0     |      | 0.8         | V    |

| I <sub>IH</sub> | High level input current        | ~40-kΩ internal pulldown                                                   |       | 125  |             | μA   |

| IIL             | Low level input current         | ~40-kΩ internal pulldown                                                   |       | 20   |             | μA   |

| C <sub>IN</sub> | Input capacitance               |                                                                            |       | 2    |             | pF   |

| DIGITAL         | - OUTPUTS (SDIO, SDO)           |                                                                            |       |      |             |      |

| V <sub>OH</sub> | High level output voltage       | I <sub>OH</sub> = 250 μA                                                   | 2.8   |      |             | V    |

| V <sub>OL</sub> | Low level output voltage        | I <sub>OL</sub> = 250 μA                                                   |       |      | 0.4         | V    |

| CLOCK           | INPUTS                          |                                                                            |       |      |             |      |

| R <sub>IN</sub> | Differential input resistance   | CLKINP, CLKINN                                                             | 130   | 160  | 190         | Ω    |

| C <sub>IN</sub> | Input capacitance               | Estimated to ground from each<br>CLKIN pin, excluding soldered<br>packaged |       | 0.8  |             | pF   |

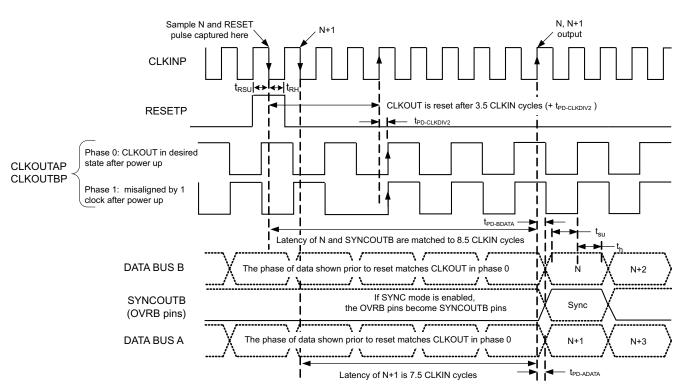

Propagation delays and setup/hold times not drawn to scale. RESET and SYNCOUT are optional. Any clock phase will work properly, but makes synchronization of data capture across multiple ADCs difficult without a known CLKOUT phase. RESET can be a single pulse (as shown), low-to-high step or repetitive pulse input signal. The frequency of repetitive RESET pulses should not exceed CLKIN/2, and should be an even divisor of CLKIN, to keep the CLKOUT phase the same with each RESET event. SYNCOUTA transitions with the same latency as the sample that is present when the RESET pulse is captured, shown here as sample N. Each RESET captured generates a SYNCOUT pulse, which behaves as a data bit. Bus B is not active in single bus mode.

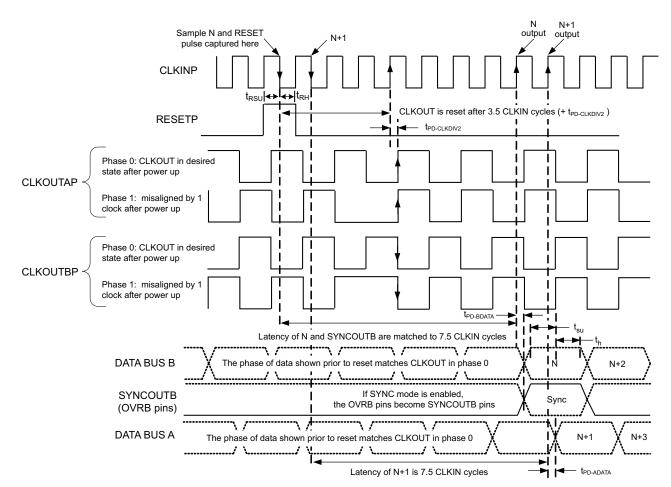

Propagation delays and setup/hold times not drawn to scale. RESET and SYNCOUT are optional. Any clock phase will work properly, but makes synchronization of data capture across multiple ADCs difficult without a known CLKOUT phase. RESET can be a single pulse (as shown), low-to-high step or repetitive pulse input signal. The frequency of repetitive RESET pulses should not exceed CLKIN/2, and should be an even divisor of CLKIN, to keep the CLKOUT phase the same with each RESET event. SYNCOUTB transitions with the same latency as the sample that is present when the RESET pulse is captured, shown here as sample N. Each RESET captured generates a SYNCOUT pulse, which behaves as a data bit.

#### Figure 2. Dual Bus Mode - Aligned, CLKOUT Divide By 2

Propagation delays and setup/hold times not drawn to scale. RESET and SYNCOUT are optional. Any clock phase will work properly, but makes synchronization of data capture across multiple ADCs difficult without a known CLKOUT phase. RESET can be a single pulse (as shown), low-to-high step or repetitive pulse input signal. The frequency of repetitive RESET pulses should not exceed CLKIN/2, and should be an even divisor of CLKIN, to keep the CLKOUT phase the same with each RESET event. SYNCOUTB transitions with the same latency as the sample that is present when the RESET pulse is captured, shown here as sample N. Each RESET captured generates a SYNCOUT pulse, which behaves as a data bit.

#### ADS5400

SLAS611C - OCTOBER 2009-REVISED JANUARY 2016

ÈXAS

NSTRUMENTS

www.ti.com

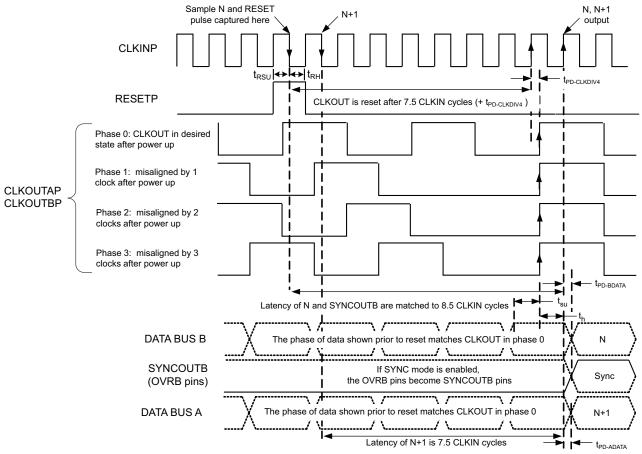

Propagation delays and setup/hold times not drawn to scale. RESET and SYNCOUT are optional. Any clock phase will work properly, but makes synchronization of data capture across multiple ADCs difficult without a known CLKOUT phase. RESET can be a single pulse (as shown), low-to-high step or repetitive pulse input signal. The frequency of repetitive RESET pulses should not exceed CLKIN/4, and should be an even divisor of CLKIN, to keep the CLKOUT phase the same with each RESET event. SYNCOUTB transitions with the same latency as the sample that is present when the RESET pulse is captured, shown here as sample N. Each RESET captured generates a SYNCOUT pulse, which behaves as a data bit.

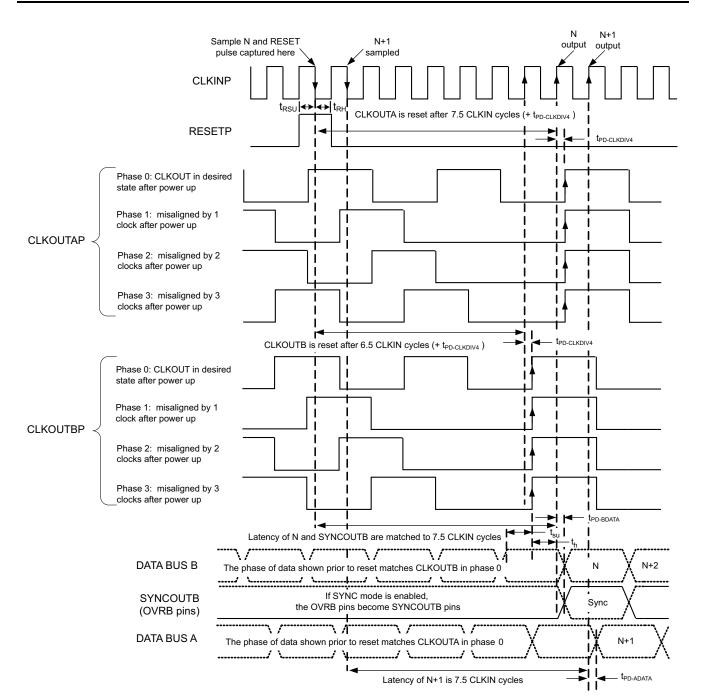

ADS5400 SLAS611C – OCTOBER 2009–REVISED JANUARY 2016

Propagation delays and setup/hold times not drawn to scale. RESET and SYNCOUT are optional. Any clock phase will work properly, but makes synchronization of data capture across multiple ADCs difficult without a known CLKOUT phase. RESET can be a single pulse (as shown), low-to-high step or repetitive pulse input signal. The frequency of repetitive RESET pulses should not exceed CLKIN/4, and should be an even divisor of CLKIN, to keep the CLKOUT phase the same with each RESET event. SYNCOUTB transitions with the same latency as the sample that is present when the RESET pulse is captured, shown here as sample N. Each RESET captured generates a SYNCOUT pulse, which behaves as a data bit.

#### Figure 5. Dual Bus Mode - Staggered, CLKOUT Divide By 4

ADS5400

SLAS611C - OCTOBER 2009-REVISED JANUARY 2016

www.ti.com

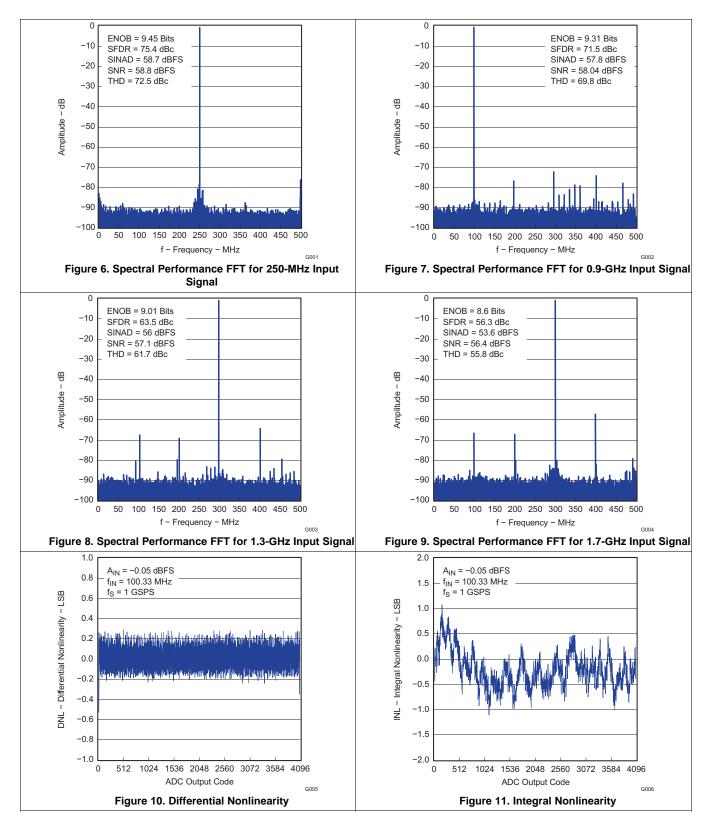

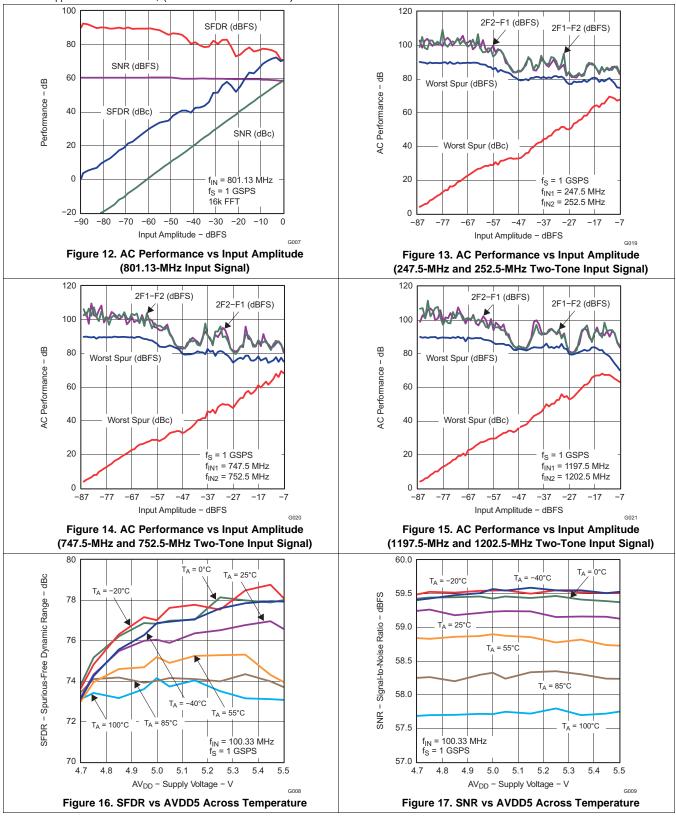

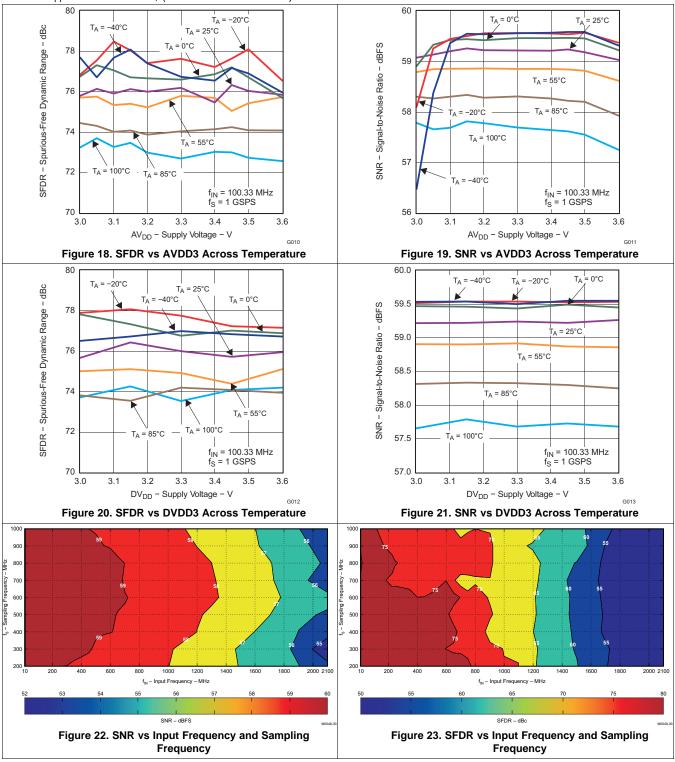

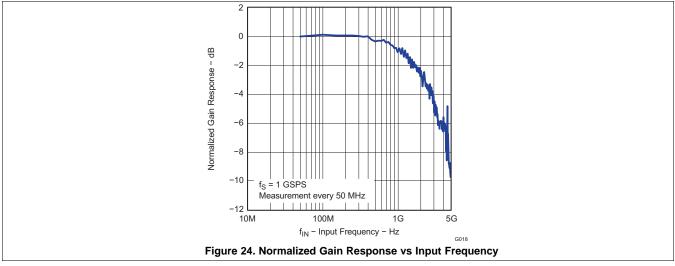

### 6.9 Typical Characteristics

#### **Typical Characteristics (continued)**

# **Typical Characteristics (continued)**

# **Typical Characteristics (continued)**

# 7 Detailed Description

# 7.1 Overview

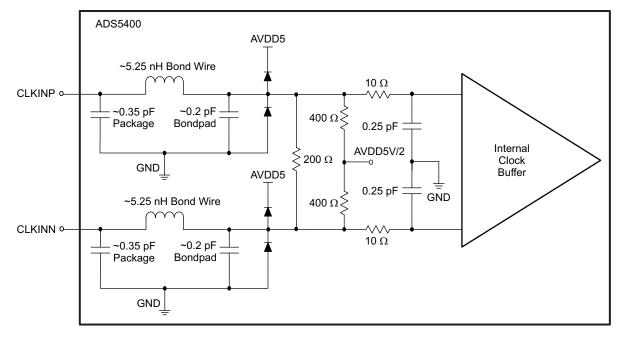

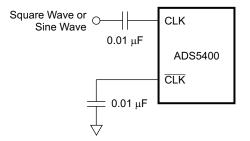

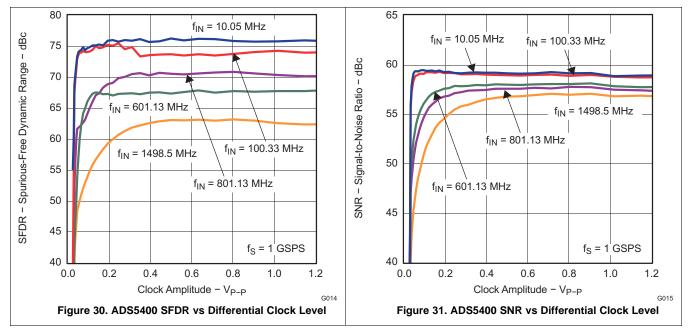

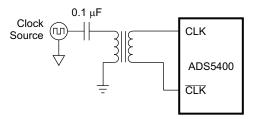

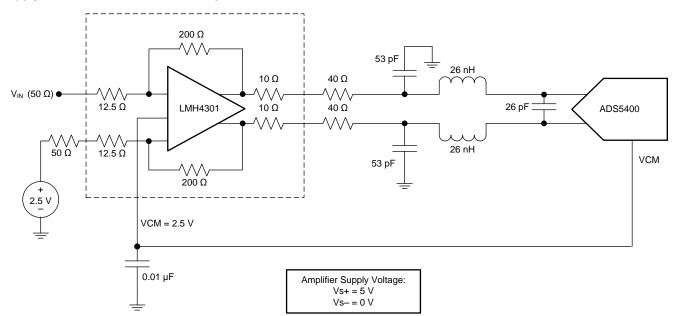

The ADS5400 is a 12-bit, 1-GSPS, monolithic pipeline ADC. Its bipolar transistor analog core operates from 5-V and 3.3-V supplies, while the output uses a 3.3-V supply to provide LVDS-compatible digital outputs. The conversion process is initiated by the falling edge of the external input clock. At the sampling instant, the differential input signal is captured by the input track-and-hold (T&H), and the input sample is sequentially converted by a series of lower resolution stages, with the outputs combined in a digital correction logic block. Both the rising and the falling clock edges are used to propagate the sample through the pipeline every half clock cycle. This process results in a data latency of 7 - 8.5 clock cycles (output mode dependent), after which the output data is available as a 12-bit parallel word, coded in offset binary or two's complement format.