ADS8671, ADS8675

SBAS779 - DECEMBER 2016

# ADS867x 14-Bit, High-Speed, Single-Supply, SAR ADC Data Acquisition System with Programmable, Bipolar Input Ranges

### 1 Features

- 14-Bit ADC with Integrated Analog Front-End

- High Speed:

- ADS8671: 1 MSPSADS8675: 500 kSPS

- Software Programmable Input Ranges:

- Bipolar Ranges: ±12.288 V, ±10.24 V, ±6.144 V, ±5.12 V, and ±2.56 V

- Unipolar Ranges: 0 V–12.288 V, 0 V–10.24 V, 0 V–6.144 V, and 0 V–5.12 V

- 5-V Analog Supply: 1.65-V to 5-V I/O Supply

- Constant Resistive Input Impedance ≥ 1 MΩ

- Input Overvoltage Protection: Up to ±20 V

- On-Chip, 4.096-V Reference with Low Drift

- · Excellent Performance:

- DNL: ±0.25 LSB; INL: ±0.4 LSB

- SNR: 84.5 dB; THD: –105 dB

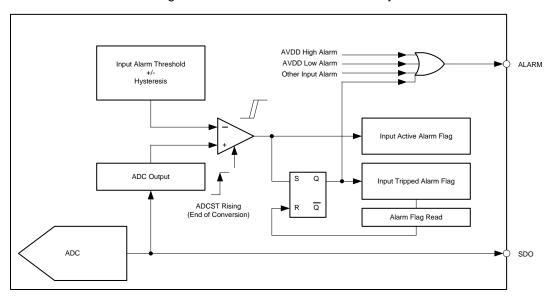

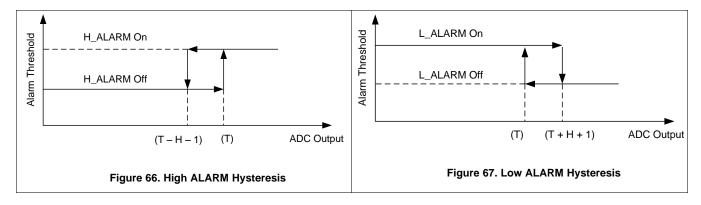

- ALARM → High, Low Thresholds per Channel

- multiSPI™ Interface with Daisy-Chain

- Extended Industrial Temperature Range: -40°C to +125°C

# 2 Applications

- Channel-Isolated PLC Analog Input Modules

- Test and Measurement

- Battery Pack Monitoring

# 3 Description

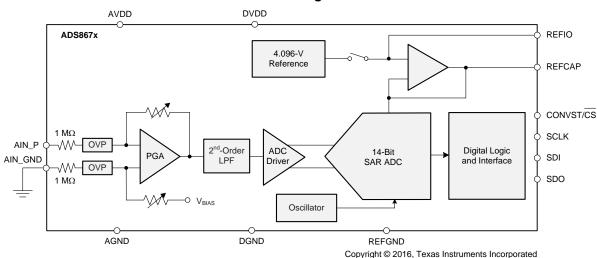

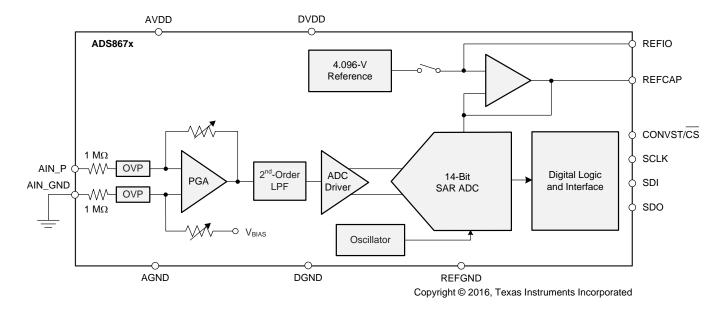

The ADS8671 and ADS8675 devices belong to a family of integrated data acquisition system based on a successive approximation (SAR) analog-to-digital converter (ADC). The devices feature a high-speed, high-precision SAR ADC, integrated analog front-end (AFE) input driver circuit, overvoltage protection circuit up to ±20 V, and an on-chip 4.096-V reference with extremely low temperature drift.

The devices operate on a single 5-V analog supply, but support true bipolar input ranges of  $\pm 12.288$  V,  $\pm 6.144$  V,  $\pm 10.24$  V,  $\pm 5.12$  V, and  $\pm 2.56$  V, as well as unipolar input ranges of 0 V to 12.288 V, 0 V to 10.24 V, 0 V to 6.144 V, and 0 V to 5.12 V. The gain and offset errors are accurately trimmed within the specified values for each input range to ensure high dc precision. The input range selection is done by software programming of the device internal registers. The devices offer a high resistive input impedance ( $\geq$  1 M $\Omega$ ) irrespective of the selected input range.

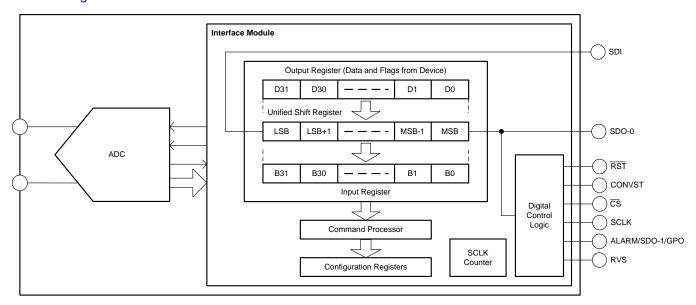

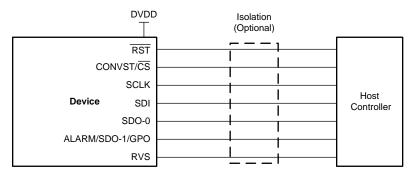

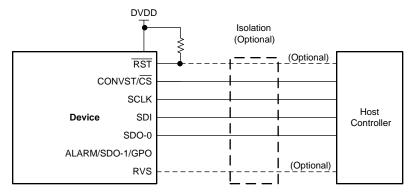

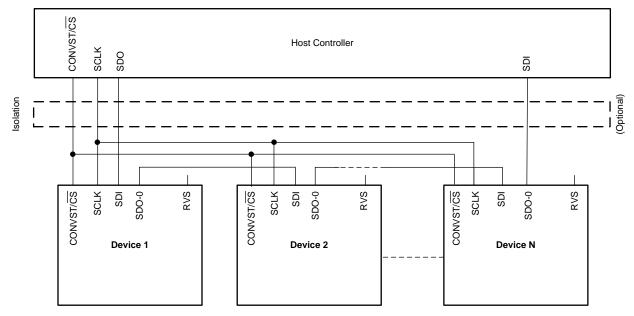

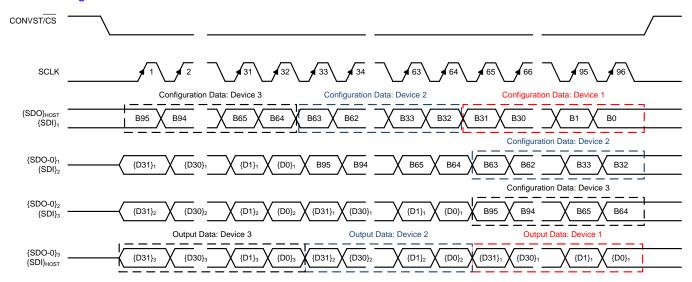

The multiSPI digital interface is backward-compatible to the traditional SPI protocol. Additionally, configurable features simplify interface to a wide range of host controllers.

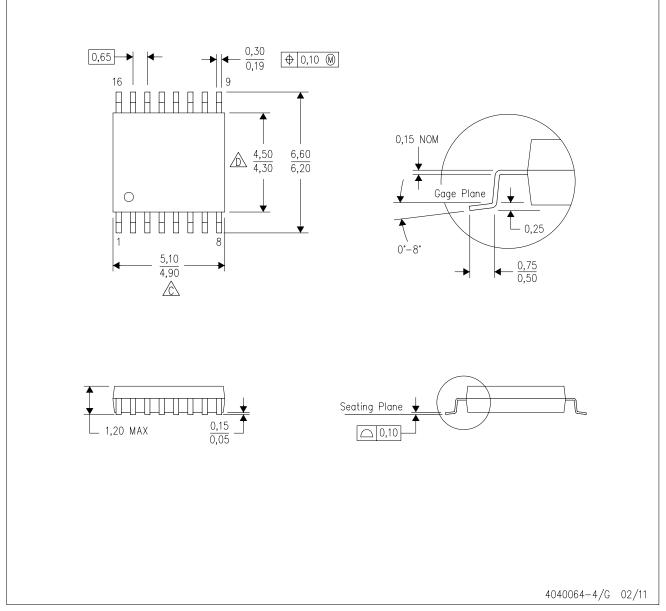

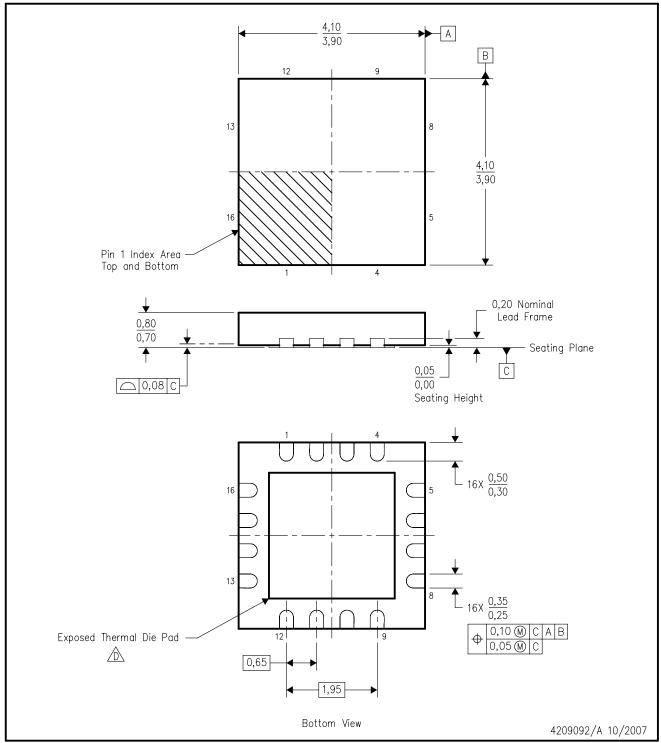

# **Device Information**(1)

| PART NUMBER | PACKAGE    | BODY SIZE (NOM)   |

|-------------|------------|-------------------|

| ADS867x     | TSSOP (16) | 5.00 mm × 4.40 mm |

| AD3007X     | WQFN (16)  | 4.00 mm × 4.00 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

#### **Block Diagram**

# **Table of Contents**

| 1 | Features 1                                          |    | 7.3 Feature Description                              | . 22 |

|---|-----------------------------------------------------|----|------------------------------------------------------|------|

| 2 | Applications 1                                      |    | 7.4 Device Functional Modes                          | . 34 |

| 3 | Description 1                                       |    | 7.5 Programming                                      | . 39 |

| 4 | Revision History2                                   |    | 7.6 Register Maps                                    | . 47 |

| 5 | Pin Configuration and Functions                     | 8  | Application and Implementation                       | 55   |

| 6 | Specifications                                      |    | 8.1 Application Information                          | . 55 |

| U | •                                                   |    | 8.2 Typical Application                              | . 55 |

|   | 6.1 Absolute Maximum Ratings 4 6.2 ESD Ratings      | 9  | Power Supply Recommendations                         | 58   |

|   | 6.3 Recommended Operating Conditions                |    | 9.1 Power Supply Decoupling                          | . 58 |

|   | 6.4 Thermal Information                             |    | 9.2 Power Saving                                     | . 58 |

|   | 6.5 Electrical Characteristics                      | 10 | Layout                                               | 59   |

|   | 6.6 Timing Requirements: Conversion Cycle           |    | 10.1 Layout Guidelines                               |      |

|   | 6.7 Timing Requirements: Asynchronous Reset 9       |    | 10.2 Layout Example                                  | . 60 |

|   | 6.8 Timing Requirements: SPI-Compatible Serial      | 11 | Device and Documentation Support                     |      |

|   | Interface9                                          |    | 11.1 Documentation Support                           |      |

|   | 6.9 Timing Requirements: Source-Synchronous Serial  |    | 11.2 Related Links                                   |      |

|   | Interface (External Clock)10                        |    | 11.3 Receiving Notification of Documentation Updates | 61   |

|   | 6.10 Timing Requirements: Source-Synchronous Serial |    | 11.4 Community Resources                             |      |

|   | Interface (Internal Clock)10                        |    | 11.5 Trademarks                                      | . 61 |

|   | 6.11 Typical Characteristics                        |    | 11.6 Electrostatic Discharge Caution                 | . 61 |

| 7 | Detailed Description                                |    | 11.7 Glossary                                        |      |

|   | 7.1 Overview                                        | 12 | Mechanical, Packaging, and Orderable                 |      |

|   | 7.2 Functional Block Diagram 21                     |    | Information                                          | 62   |

# 4 Revision History

| DATE          | REVISION | NOTES            |

|---------------|----------|------------------|

| December 2016 | *        | Initial release. |

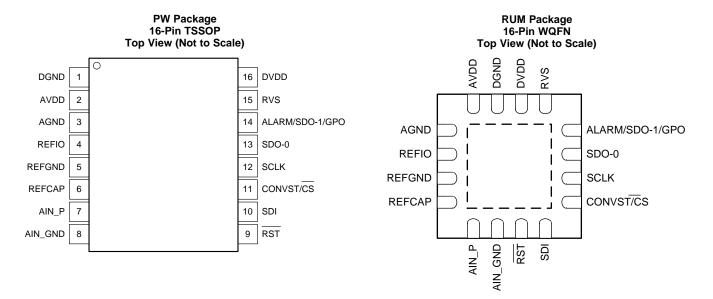

# 5 Pin Configuration and Functions

### **Pin Functions**

| NAME            | N     | NO.  |                     | PERCENTION                                                                                                                                                                                                                                                                                                                                            |

|-----------------|-------|------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME            | TSSOP | WQFN | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                           |

| AGND            | 3     | 1    | Р                   | Analog ground pin. Decouple with the AVDD pin.                                                                                                                                                                                                                                                                                                        |

| AIN_GND         | 8     | 6    | Al                  | Analog input: negative. Decouple with the AIN_P pin.                                                                                                                                                                                                                                                                                                  |

| AIN_P           | 7     | 5    | Al                  | Analog input: positive. Decouple with the AIN_GND pin.                                                                                                                                                                                                                                                                                                |

| ALARM/SDO-1/GPO | 14    | 12   | DO                  | Multi-function output pin. Active high alarm. Data output 1 for serial communication. General-purpose output pin.                                                                                                                                                                                                                                     |

| AVDD            | 2     | 16   | Р                   | Analog supply pin. Decouple with the AGND pin.                                                                                                                                                                                                                                                                                                        |

| CONVST/CS       | 11    | 9    | DI                  | Dual-functionality pin.  Active high logic: conversion start input pin; a CONVST rising edge brings the device from acquisition phase to conversion phase.  Active low logic: chip-select input pin; the device takes control of the data bus when $\overline{\text{CS}}$ is low; the SDO-x pins go to tri-state when $\overline{\text{CS}}$ is high. |

| DGND            | 1     | 15   | Р                   | Digital ground pin. Decouple with the DVDD pin.                                                                                                                                                                                                                                                                                                       |

| DVDD            | 16    | 14   | Р                   | Digital supply pin. Decouple with the DGND pin.                                                                                                                                                                                                                                                                                                       |

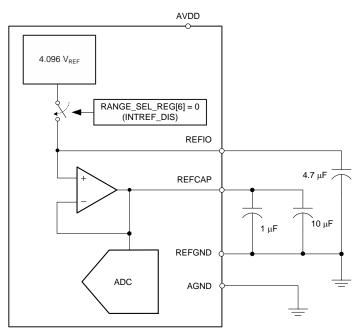

| REFCAP          | 6     | 4    | AO                  | ADC reference buffer decoupling capacitor pin. Decouple with the REFGND pin.                                                                                                                                                                                                                                                                          |

| REFGND          | 5     | 3    | Р                   | Reference ground pin; short to the analog ground plane. Decouple with the REFIO and REFCAP pins.                                                                                                                                                                                                                                                      |

| REFIO           | 4     | 2    | AIO                 | Internal reference output and external reference input pin. Decouple with REFGND.                                                                                                                                                                                                                                                                     |

| RST             | 9     | 7    | DI                  | Active low logic input to reset the device.                                                                                                                                                                                                                                                                                                           |

| RVS             | 15    | 13   | DO                  | Multi-function output pin for serial interface; see the <i>RESET State</i> section. With $\overline{CS}$ held high, RVS reflects the status of the internal ADCST signal. With $\overline{CS}$ low, the status of RVS depends on the output protocol selection.                                                                                       |

| SCLK            | 12    | 10   | DI                  | Serial communication: clock input pin for the serial interface. All system-synchronous data transfer protocols are timed with respect to the SCLK signal.                                                                                                                                                                                             |

| SDI             | 10    | 8    | DI                  | Dual function: data input pin for serial communication. Chain data input during serial communication in daisy-chain mode.                                                                                                                                                                                                                             |

| SDO-0           | 13    | 11   | DO                  | Serial communication: data output 0                                                                                                                                                                                                                                                                                                                   |

<sup>(1)</sup> AI = analog input, AIO = analog input/output, DI = digital input, DO = digital output, and P = power supply.

# TEXAS INSTRUMENTS

# 6 Specifications

#### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                        |                                                                                                                  | MIN  | MAX        | UNIT |

|----------------------------------------|------------------------------------------------------------------------------------------------------------------|------|------------|------|

| AINL D. AINL CND to CND                | AVDD = 5 V <sup>(2)</sup>                                                                                        | -20  | 20         | V    |

| AIN_P, AIN_GND to GND                  | _GND to GND AVDD = floating (3)  ND or DVDD to GND  REFGND or REFIO to REFGND  =GND  pins to GND  at pins to GND | -11  | 11         | V    |

| AVDD to GND or DVDD to GND             |                                                                                                                  | -0.3 | 7          | V    |

| REFCAP to REFGND or REFIO to REFGND    |                                                                                                                  | -0.3 | 5.7        | V    |

| GND to REFGND                          |                                                                                                                  | -0.3 | 0.3        | V    |

| Digital input pins to GND              |                                                                                                                  | -0.3 | DVDD + 0.3 | V    |

| Digital output pins to GND             |                                                                                                                  | -0.3 | DVDD + 0.3 | V    |

| Tomporaturo                            | Operating, T <sub>A</sub>                                                                                        | -40  | 125        | °C   |

| Digital output pins to GND Temperature | Storage, T <sub>stg</sub>                                                                                        | -65  | 150        | C    |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### 6.2 ESD Ratings

|                             |                                                                   |                                                                                    |                        | VALUE | UNIT |

|-----------------------------|-------------------------------------------------------------------|------------------------------------------------------------------------------------|------------------------|-------|------|

| V Flanton etakin dinah aura | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup> | Analog input pins (AIN_P, AIN_GND)                                                 | ±4000                  |       |      |

| $V_{(ESD)}$                 | Electrostatic discharge                                           | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup> (AIN_P, AIN_GND) | ±2000                  | V     |      |

|                             |                                                                   | Charged device model (CDM), per JEDEC specification JESD2                          | 22-C101 <sup>(2)</sup> | ±500  |      |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

### 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|      |                        | MIN  | NOM | MAX  | UNIT |

|------|------------------------|------|-----|------|------|

| AVDD | Analog supply voltage  | 4.75 | 5   | 5.25 | V    |

| DVDD | Digital supply voltage | 1.65 | 3.3 | AVDD | V    |

#### 6.4 Thermal Information

|                      |                                              | ADS8671    | ADS8671, ADS8675 |      |  |

|----------------------|----------------------------------------------|------------|------------------|------|--|

|                      | THERMAL METRIC <sup>(1)</sup>                | PW (TSSOP) | RUM (WQFN)       | UNIT |  |

|                      |                                              | 16 PINS    | 16 PINS          |      |  |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 95.7       | 31.9             | °C/W |  |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 29.3       | 27.9             | °C/W |  |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 41.5       | 7.4              | °C/W |  |

| ΨЈТ                  | Junction-to-top characterization parameter   | 1.5        | 0.3              | °C/W |  |

| ΨЈВ                  | Junction-to-board characterization parameter | 40.8       | 7.4              | °C/W |  |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | N/A        | 1.9              | °C/W |  |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

Product Folder Links: ADS8671 ADS8675

<sup>(2)</sup> AVDD = 5 V offers a low impedance of  $< 30 \text{ k}\Omega$ .

<sup>(3)</sup> AVDD = floating with an impedance > 30 k $\Omega$ .

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 6.5 Electrical Characteristics

all minimum and maximum specifications are at  $T_A = -40^{\circ}$ C to +125°C; typical specifications are at  $T_A = 25^{\circ}$ C; AVDD = 5 V, DVDD = 3.3 V,  $V_{DEE} = 4.096$  V (internal), and maximum throughput (unless otherwise noted)

|                  | PARAMETER                                                                  |                                      |                                                                   | TEST CONDITIONS                            | MIN              | TYP                      | MAX    | UNIT   |  |

|------------------|----------------------------------------------------------------------------|--------------------------------------|-------------------------------------------------------------------|--------------------------------------------|------------------|--------------------------|--------|--------|--|

| ANALOG INP       | PUTS                                                                       |                                      |                                                                   |                                            |                  |                          |        |        |  |

|                  |                                                                            |                                      | Input range = :                                                   | ±3 × V <sub>REF</sub>                      | -12.288          |                          | 12.288 |        |  |

|                  |                                                                            |                                      | Input range = :                                                   | Input range = ±2.5 × V <sub>REF</sub>      |                  |                          | 10.24  |        |  |

|                  | , Full-scale input span <sup>(1)</sup><br><sup>IN</sup> (AIN_P to AIN_GND) |                                      | Input range = ±1.5 x V <sub>REF</sub>                             |                                            | -6.144           |                          | 6.144  |        |  |

|                  |                                                                            |                                      | Input range = :                                                   | ±1.25 × V <sub>REF</sub>                   | -5.12            |                          | 5.12   |        |  |

| V <sub>IN</sub>  | Full-scale input span <sup>(1)</sup>                                       |                                      | Input range = :                                                   | ±0.625 × V <sub>REF</sub>                  | -2.56            |                          | 2.56   | ٧      |  |

|                  | (AIN_I TO AIN_OND)                                                         |                                      | Input range = 3                                                   | 3 × V <sub>REF</sub>                       | 0                |                          | 12.288 |        |  |

|                  |                                                                            |                                      | Input range = 2                                                   | 2.5 × V <sub>REF</sub>                     | 0                |                          | 10.24  |        |  |

|                  |                                                                            |                                      | Input range =                                                     | 1.5 × V <sub>REF</sub>                     | 0                |                          | 6.144  |        |  |

|                  |                                                                            |                                      | Input range =                                                     | 1.25 × V <sub>REF</sub>                    | 0                |                          | 5.12   |        |  |

|                  |                                                                            |                                      | Input range = :                                                   | ±3 × V <sub>REF</sub>                      | -12.288          |                          | 12.288 |        |  |

|                  |                                                                            |                                      | Input range = :                                                   | ±2.5 × V <sub>REF</sub>                    | -10.24           |                          | 10.24  |        |  |

|                  |                                                                            |                                      | Input range = :                                                   | ±1.5 × V <sub>REF</sub>                    | -6.144           |                          | 6.144  |        |  |

| AIN_P            |                                                                            |                                      | Input range = :                                                   | ±1.25 × V <sub>REF</sub>                   | -5.12            |                          | 5.12   |        |  |

|                  | Operating input range                                                      |                                      | Input range = :                                                   | ±0.625 × V <sub>REF</sub>                  | -2.56            |                          | 2.56   | V      |  |

|                  |                                                                            |                                      | Input range = 3                                                   | 3 × V <sub>REF</sub>                       | 0                |                          | 12.288 |        |  |

|                  |                                                                            | Input range = 2                      | 2.5 × V <sub>REF</sub>                                            | 0                                          |                  | 10.24                    |        |        |  |

|                  |                                                                            | Input range = 1.5 × V <sub>REF</sub> |                                                                   | 0                                          |                  | 6.144                    |        |        |  |

|                  |                                                                            |                                      | Input range =                                                     | 1.25 × V <sub>REF</sub>                    | 0                |                          | 5.12   |        |  |

| AIN_GND          | Operating input range                                                      |                                      | All input range                                                   | es .                                       | -0.1             | 0                        | 0.1    | V      |  |

|                  | Input impedance                                                            | At T <sub>A</sub> = 25°C             |                                                                   | Input range = ±3 × V <sub>REF</sub>        | 1.02             | 1.2                      | 1.38   |        |  |

|                  |                                                                            |                                      | Input range = ±1.5 × V <sub>REF</sub>                             | 1.02                                       | 1.2              | 1.38                     | -      |        |  |

|                  |                                                                            |                                      | Input range = 3 × V <sub>REF</sub>                                | 1.02                                       | 1.2              | 1.38                     |        |        |  |

|                  |                                                                            |                                      |                                                                   | Input range = 1.5 × V <sub>REF</sub>       | 1.02             | 1.2                      | 1.38   | -      |  |

| R <sub>IN</sub>  |                                                                            |                                      | At T <sub>A</sub> = 25°C                                          | Input range = ±2.5 × V <sub>RFF</sub>      | 0.85             | 1                        | 1.15   |        |  |

|                  |                                                                            |                                      |                                                                   | Input range = ±1.25 × V <sub>REF</sub>     | 0.85             | 1                        | 1.15   |        |  |

|                  |                                                                            |                                      |                                                                   | Input range = ±0.625 × V <sub>REF</sub>    | 0.85             | 1                        | 1.15   |        |  |

|                  |                                                                            |                                      |                                                                   | Input range = 2.5 × V <sub>REF</sub>       | 0.85             | 1                        | 1.15   |        |  |

|                  |                                                                            |                                      | Input range = 1.25 × V <sub>REF</sub>                             | 0.85                                       | 1                | 1.15                     | -      |        |  |

|                  | Input impedance drift                                                      |                                      |                                                                   |                                            |                  | 7                        | 25     | ppm/°( |  |

|                  |                                                                            |                                      |                                                                   | Input range = ±3 × V <sub>REF</sub>        | (V <sub>IN</sub> | – 2.5) / R <sub>IN</sub> |        |        |  |

|                  |                                                                            |                                      |                                                                   | Input range = ±2.5 × V <sub>RFF</sub>      |                  | – 2.2) / R <sub>IN</sub> |        | -      |  |

|                  |                                                                            |                                      |                                                                   | Input range = ±1.5 × V <sub>REF</sub>      |                  | – 2.0) / R <sub>IN</sub> |        | 1      |  |

|                  |                                                                            |                                      | \\/ith\\\altaga                                                   | Input range = $\pm 1.25 \times V_{REF}$    |                  | – 2.0) / R <sub>IN</sub> |        | -      |  |

| I <sub>IN</sub>  | Input current                                                              |                                      | With voltage<br>at the AIN_P                                      | Input range = $\pm 0.625 \times V_{REF}$   |                  | – 1.6) / R <sub>IN</sub> |        | μA     |  |

|                  | ·                                                                          |                                      | pin = V <sub>IN</sub>                                             | Input range = 3 x V <sub>REF</sub>         |                  | – 2.6) / R <sub>IN</sub> |        |        |  |

|                  |                                                                            |                                      |                                                                   | Input range = 2.5 × V <sub>REF</sub>       |                  | – 2.5) / R <sub>IN</sub> |        |        |  |

|                  |                                                                            |                                      |                                                                   | Input range = 1.5 × V <sub>REF</sub>       |                  | - 2.7) / R <sub>IN</sub> |        |        |  |

|                  |                                                                            |                                      |                                                                   | Input range = 1.25 × V <sub>RFF</sub>      |                  | – 2.5) / R <sub>IN</sub> |        | -      |  |

| NPUT OVER        | VOLTAGE PROTECTION CIRC                                                    | UIT                                  |                                                                   |                                            |                  | ,                        |        |        |  |

|                  | •                                                                          |                                      | AVDD = 5 V o all input range                                      | r offers low impedance < 30 k $\Omega$ , s | -20              |                          | 20     | .,     |  |

| V <sub>OVP</sub> | All input ranges                                                           |                                      | AVDD = floating with impedance > 30 k $\Omega$ , all input ranges |                                            | -11              |                          | 11     | V      |  |

| NPUT BAND        | WIDTH                                                                      |                                      |                                                                   |                                            |                  |                          |        |        |  |

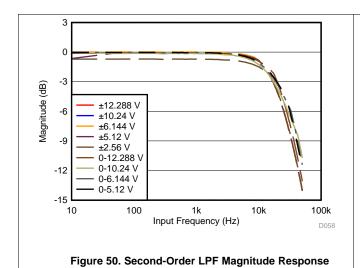

| f_3 dB           | Small-signal Input                                                         | -3 dB                                | All input range                                                   | S                                          |                  | 15                       |        |        |  |

| f_0.1 dB         | bandwidth                                                                  | -0.1 dB                              | All input range                                                   | is a                                       |                  | 2.5                      |        | kHz    |  |

<sup>(1)</sup> Ideal input span, does not include gain or offset error.

Copyright © 2016, Texas Instruments Incorporated Product Folder Links: ADS8671 ADS8675

# TEXAS INSTRUMENTS

# **Electrical Characteristics (continued)**

all minimum and maximum specifications are at  $T_A = -40$ °C to +125°C; typical specifications are at  $T_A = 25$ °C; AVDD = 5 V, DVDD = 3.3 V,  $V_{REF} = 4.096$  V (internal), and maximum throughput (unless otherwise noted)

|                | PARAMETER                                  |                                         | TEST CONDITIONS                          | MIN      | TYP   | MAX   | UNIT   |

|----------------|--------------------------------------------|-----------------------------------------|------------------------------------------|----------|-------|-------|--------|

| SYSTEM PE      | RFORMANCE                                  | '                                       |                                          | <u> </u> |       |       |        |

|                | Resolution                                 |                                         |                                          | 14       |       |       | Bits   |

| NMC            | No missing codes                           |                                         |                                          | 14       |       |       | Bits   |

| DNL            | Differential nonlinearity (2)              | All input range                         | S                                        | -0.6     | ±0.25 | 0.6   | LSB    |

| INL            | Integral nonlinearity (2)                  | All input range                         | 5                                        | -0.75    | ±0.4  | 0.75  | LSB    |

| _              | Offset error <sup>(3)</sup>                | A4.T. 0500                              | All bipolar ranges <sup>(4)</sup>        | -1       | ±0.2  | 1     | \/     |

| E <sub>O</sub> | Offset error 47                            | At $T_A = 25^{\circ}C$                  | All unipolar ranges <sup>(5)</sup>       | -2       | ±0.2  | 2     | mV     |

|                | Offset error drift with temperature        | All input range                         | S                                        | -3       | ±0.75 | 3     | ppm/°C |

| E <sub>G</sub> | Gain error <sup>(6)</sup>                  | At T <sub>A</sub> = 25°C, a             | all input ranges                         | -0.025   | ±0.01 | 0.025 | %FSR   |

|                | Gain error drift with temperature (7)      | All input range                         | S                                        | -5       | ±1    | 5     | ppm/°C |

| DYNAMIC C      | HARACTERISTICS                             |                                         |                                          |          |       |       |        |

|                |                                            | Input range = ±                         | ±3 × V <sub>REF</sub>                    | 84       | 84.5  |       |        |

|                |                                            | Input range = ±2.5 x V <sub>REF</sub>   |                                          | 84       | 84.5  |       |        |

|                |                                            | Input range = ±                         | Input range = $\pm 1.5 \times V_{REF}$   |          | 84.25 |       |        |

|                | Signal-to-noise ratio <sup>(8)</sup>       | Input range = $\pm 1.25 \times V_{REF}$ |                                          | 83.75    | 84.25 |       |        |

| SNR            |                                            | Input range = ±                         | Input range = $\pm 0.625 \times V_{REF}$ |          | 84    |       | dB     |

|                |                                            | Input range = $3 \times V_{REF}$        |                                          | 83.5     | 84.25 |       | -      |

|                |                                            | Input range = $2.5 \times V_{REF}$      |                                          | 83.5     | 84.25 |       |        |

|                |                                            | Input range = $1.5 \times V_{REF}$      |                                          | 83.25    | 84    |       |        |

|                |                                            | Input range = 1.25 × V <sub>REF</sub>   |                                          | 83.25    | 84    |       |        |

| THD            | Total harmonic distortion (9) (8)          | All input range                         | S                                        |          | -105  |       | dB     |

|                |                                            | Input range = =                         | ±3 × V <sub>REF</sub>                    | 83.9     | 84.5  |       |        |

|                |                                            | Input range = :                         | £2.5 × V <sub>REF</sub>                  | 83.9     | 84.5  |       |        |

|                |                                            | Input range = :                         | ±1.5 × V <sub>REF</sub>                  | 83.65    | 84.25 |       |        |

|                |                                            | Input range = :                         | ±1.25 × V <sub>REF</sub>                 | 83.65    | 84.25 |       | dB     |

| SINAD          | Signal-to-noise + distortion (8)           | Input range = =                         | ±0.625 × V <sub>REF</sub>                | 83.15    | 84    |       |        |

|                |                                            | Input range = 3                         | 3 x V <sub>REF</sub>                     | 83.4     | 84.25 |       |        |

|                |                                            | Input range = 2                         | 2.5 × V <sub>REF</sub>                   | 83.4     | 84.25 |       |        |

|                |                                            | Input range = 1                         | 1.5 × V <sub>REF</sub>                   | 83.15    | 84    |       |        |

|                |                                            | Input range = 1                         | 1.25 × V <sub>REF</sub>                  | 83.15    | 84    |       |        |

| SFDR           | Spurious-free dynamic range <sup>(8)</sup> | All input range                         | <u></u>                                  |          | 108   |       | dB     |

- (2) This specification indicates the endpoint INL, not best-fit INL.

- (3) Measured relative to actual measured reference.

- (4) Bipolar ranges are ±12.288 V, ±10.24 V, ±6.144 V, ±5.12 V, and ±2.56 V.

- (5) Unipolar ranges are 0 V-12.288 V, 0 V-10.24 V, 0 V-6.144 V, and 0 V-5.12 V.

- (6) Excludes internal reference accuracy error.

- (7) Excludes internal reference temperature drift.

- (8) All specifications expressed in decibels (dB) refer to the full-scale input (FSR) and are tested with a 1-kHz input signal 0.25 dB below full-scale, unless otherwise specified.

- (9) Calculated on the first nine harmonics of the input frequency.

# **Electrical Characteristics (continued)**

all minimum and maximum specifications are at  $T_A = -40$ °C to +125°C; typical specifications are at  $T_A = 25$ °C; AVDD = 5 V, DVDD = 3.3 V,  $V_{REF} = 4.096$  V (internal), and maximum throughput (unless otherwise noted)

|                          | PARAMETER                                      |                           | TEST CONDITIONS                                 | MIN   | TYP   | MAX   | UNIT   |

|--------------------------|------------------------------------------------|---------------------------|-------------------------------------------------|-------|-------|-------|--------|

| SAMPLING DY              | NAMICS                                         |                           |                                                 |       |       |       |        |

|                          |                                                | ADS8671                   |                                                 |       |       | 665   |        |

| t <sub>CONV</sub>        | Conversion time                                | ADS8675                   | ADS8675                                         |       |       | 1000  | ns     |

|                          |                                                | ADS8671                   |                                                 | 335   |       |       |        |

| t <sub>ACQ</sub>         | Acquisition time                               | ADS8675                   |                                                 | 1000  |       |       | ns     |

|                          | Maximum throughput rate                        | ADS8671                   |                                                 |       |       | 1000  |        |

| f <sub>cycle</sub>       | without latency                                | ADS8675                   |                                                 |       |       | 500   | kSPS   |

| INTERNAL RE              | FERENCE OUTPUT                                 |                           |                                                 |       |       |       |        |

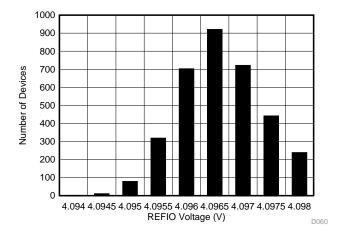

|                          | On the REFIO pin                               |                           | TSSOP (PW)                                      | 4.095 | 4.096 | 4.097 |        |

| $V_{REFIO}$              | (configured as an output)                      | At $T_A = 25^{\circ}C$    | WQFN (RUM)                                      | 4.094 | 4.096 | 4.098 | V      |

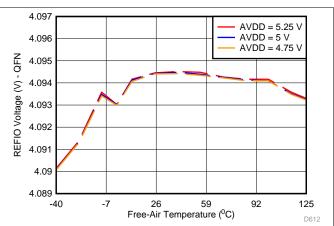

|                          |                                                | TSSOP (PW)                |                                                 |       | 4     |       |        |

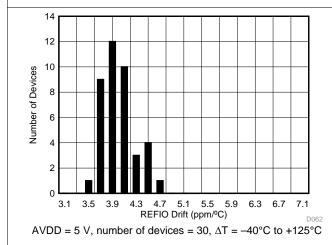

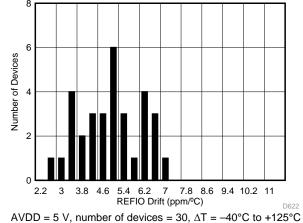

| $dV_{REFIO}/dT_{A}$      | Internal reference temperature drift           | WQFN (RUM)                |                                                 |       | 5     |       | ppm/°C |

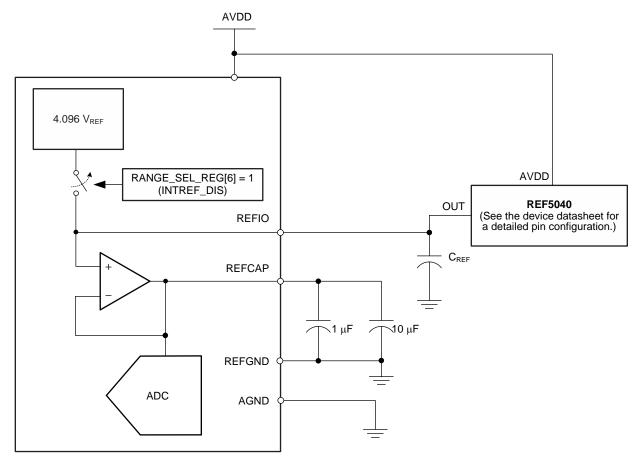

| C <sub>OUT REFIO</sub>   | Decoupling capacitor on REFIO pin              | ( - ,                     |                                                 | 4.7   |       |       | μF     |

|                          | Reference voltage to the ADC                   |                           |                                                 |       |       |       | -      |

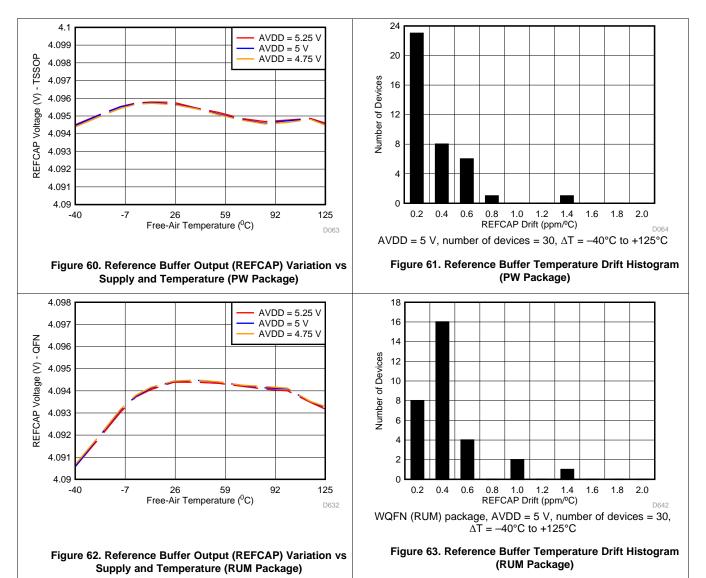

| V <sub>REFCAP</sub>      | (on the REFCAP pin)                            | At $T_A = 25^{\circ}C$    |                                                 | 4.095 | 4.096 | 4.097 | V      |

|                          | REFCAP temperature drift                       |                           |                                                 |       | 0.5   | 2     | ppm/°C |

| $C_{\text{OUT\_REFCAP}}$ | Decoupling capacitor on REFCAP pin             |                           |                                                 | 10    |       |       | μF     |

|                          | Turn-on time                                   | C <sub>OUT_REFCAP</sub> = | 10 $\mu$ F, C <sub>OUT_REFIO</sub> = 10 $\mu$ F |       | 20    |       | ms     |

| EXTERNAL RE              | EFERENCE INPUT                                 |                           |                                                 | ·     |       |       |        |

| $V_{REFIO\_EXT}$         | External reference voltage on REFIO            | REFIO pin cor             | nfigured as an input                            | 4.046 | 4.096 | 4.146 | V      |

| AVDD COMPA               | RATOR                                          |                           |                                                 | ·     |       |       |        |

| V <sub>TH_HIGH</sub>     | High threshold voltage                         |                           |                                                 |       | 5.3   |       | V      |

| V <sub>TH_LOW</sub>      | Low threshold voltage                          |                           |                                                 |       | 4.7   |       | V      |

| POWER-SUPP               | PLY REQUIREMENTS                               |                           |                                                 |       |       |       |        |

| AVDD                     | Analog power-supply voltage                    |                           |                                                 | 4.75  | 5     | 5.25  |        |

| 21/22                    | 5                                              | Operating rang            | je                                              | 1.65  | 3.3   | AVDD  | V      |

| DVDD                     | Digital power-supply voltage                   | Supply range t            | Supply range for specified performance          |       | 3.3   | AVDD  |        |

|                          |                                                | Internal                  | ADS8671                                         |       | 6.7   | 8.6   |        |

|                          | Analog supply current,                         | reference                 | ADS8675                                         |       | 5.25  | 6.75  |        |

| I <sub>AVDD_DYN</sub>    | device converting at maximum<br>throughput     | External                  | ADS8671                                         |       | 5.5   | 7     | mA     |

|                          |                                                | reference                 | ADS8675                                         |       | 4     | 5     |        |

|                          | Analog supply current,                         | Internal refere           | nce                                             |       | 2.9   | 4     |        |

| I <sub>AVDD_STC</sub>    | device not converting                          | External refere           | ence                                            |       | 1.7   | 2.25  | mA     |

|                          | Analog supply current,                         | Internal refere           | nce                                             |       | 2.8   |       |        |

| I <sub>AVDD_STDBY</sub>  | device in STANDBY mode                         | External refere           | ence                                            |       | 1.6   |       | mA     |

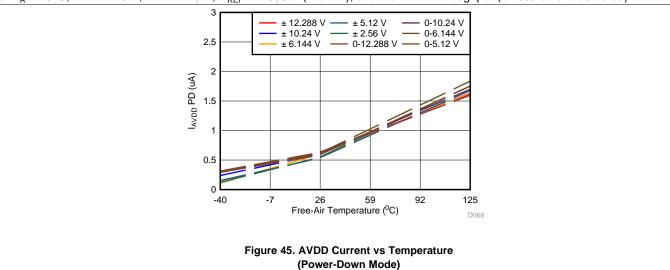

|                          | Analog supply current,                         | Internal refere           | nce                                             |       | 10    |       |        |

| I <sub>AVDD_PD</sub>     | device in PD mode                              | External refere           |                                                 |       | 10    |       | μА     |

| I <sub>DVDD_DYN</sub>    | Digital supply current, maximum throughput     |                           |                                                 |       | 0.2   | 0.25  | mA     |

| I <sub>DVDD_STDBY</sub>  | Digital supply current, device in STANDBY mode |                           |                                                 |       | 1     |       | μА     |

| I <sub>DVDD_PD</sub>     | Digital supply current, device in PD mode      |                           |                                                 |       | 1     |       | μА     |

# TEXAS INSTRUMENTS

# **Electrical Characteristics (continued)**

all minimum and maximum specifications are at  $T_A = -40$ °C to +125°C; typical specifications are at  $T_A = 25$ °C; AVDD = 5 V, DVDD = 3.3 V,  $V_{REF} = 4.096$  V (internal), and maximum throughput (unless otherwise noted)

|                 | PARAMETER                               | TEST CONDITIONS                | MIN           | TYP MAX       | UNIT |

|-----------------|-----------------------------------------|--------------------------------|---------------|---------------|------|

| DIGITAL II      | NPUTS (CMOS)                            |                                |               |               |      |

| V               | Digital high inputs of the part level   | DVDD > 2.35 V                  | 0.7 ×<br>DVDD | DVDD +<br>0.3 | V    |

| V <sub>IH</sub> | Digital high input voltage logic level  | DVDD ≤ 2.35 V                  | 0.8 ×<br>DVDD | DVDD +<br>0.3 | V    |

| V               | Digital law input valtage legis level   | DVDD > 2.35 V                  | -0.3          | 0.3 ×<br>DVDD | V    |

| V <sub>IL</sub> | Digital low input voltage logic level   | DVDD ≤ 2.35 V                  | -0.3          | 0.2 ×<br>DVDD | V    |

|                 | Input leakage current                   |                                |               | 100           | nA   |

|                 | Input pin capacitance                   |                                |               | 5             | pF   |

| DIGITAL C       | DUTPUTS (CMOS)                          |                                |               |               |      |

| $V_{OH}$        | Digital high output voltage logic level | I <sub>O</sub> = 500-μA source | 0.8 ×<br>DVDD | DVDD          | V    |

| V <sub>OL</sub> | Digital low output voltage logic level  | I <sub>O</sub> = 500-μA sink   | 0             | 0.2 ×<br>DVDD | V    |

|                 | Floating state leakage current          | Only for digital output pins   |               | 1             | μA   |

|                 | Internal pin capacitance                |                                |               | 5             | pF   |

| TEMPERA         | TURE RANGE                              |                                | •             |               | •    |

| T <sub>A</sub>  | Operating free-air temperature          |                                | -40           | 125           | °C   |

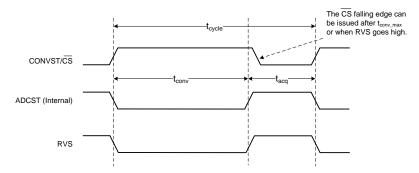

# 6.6 Timing Requirements: Conversion Cycle

all minimum and maximum specifications are at  $T_A = -40$ °C to +125°C; typical specifications are at  $T_A = 25$ °C; AVDD = 5 V, DVDD = 3.3 V,  $V_{REF} = 4.096$  V (internal), and maximum throughput (unless otherwise noted)

|                    |                                      |         | MIN                  | TYP | MAX  | UNIT |

|--------------------|--------------------------------------|---------|----------------------|-----|------|------|

| TIMING             | REQUIREMENTS                         |         |                      |     |      |      |

| f <sub>cycle</sub> | Sampling frequency  ADS8671  ADS8675 | ADS8671 |                      |     | 1000 | kSPS |

|                    |                                      | ADS8675 |                      |     | 500  |      |

| t <sub>cycle</sub> | ADC cycle time period                |         | 1/f <sub>cycle</sub> |     |      |      |

| t <sub>acq</sub>   | Acquisition time                     | ADS8671 | 335                  |     |      |      |

|                    |                                      | ADS8675 | 1000                 |     |      | ns   |

| TIMING             | SPECIFICATIONS                       |         | ·                    |     |      |      |

| t <sub>conv</sub>  | Conversion time                      | ADS8671 |                      |     | 665  |      |

|                    |                                      | ADS8675 |                      |     | 1000 | ns   |

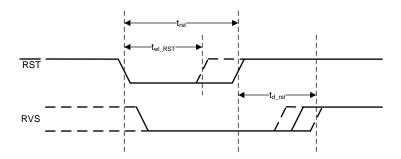

# 6.7 Timing Requirements: Asynchronous Reset

all minimum and maximum specifications are at  $T_A = -40$ °C to +125°C; typical specifications are at  $T_A = 25$ °C; AVDD = 5 V, DVDD = 3.3 V,  $V_{REF} = 4.096$  V (internal), and maximum throughput (unless otherwise noted)

|                        | , 1121                                                           |     |     |     |      |

|------------------------|------------------------------------------------------------------|-----|-----|-----|------|

|                        |                                                                  | MIN | TYP | MAX | UNIT |

| TIMING REG             | QUIREMENTS                                                       |     |     |     |      |

| t <sub>wl_RST</sub>    | Pulse duration: RST high                                         | 100 |     |     | ns   |

| TIMING SPE             | CIFICATIONS                                                      |     |     |     |      |

| t <sub>D_RST_POR</sub> | Delay time for POR reset: RST rising to RVS rising               |     | 20  |     | ms   |

| t <sub>D_RST_APP</sub> | Delay time for application reset: RST rising to CONVST/CS rising |     |     | 1   | μs   |

| t <sub>NAP_WKUP</sub>  | Wake-up time: NAP mode                                           |     |     | 20  | μs   |

| t <sub>PWRUP</sub>     | Power-up time: PD mode                                           |     | 20  |     | ms   |

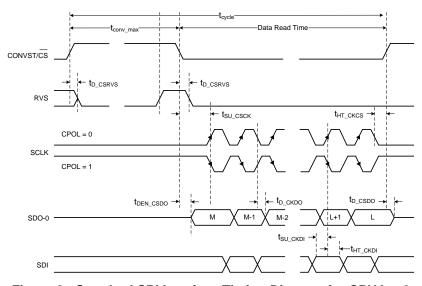

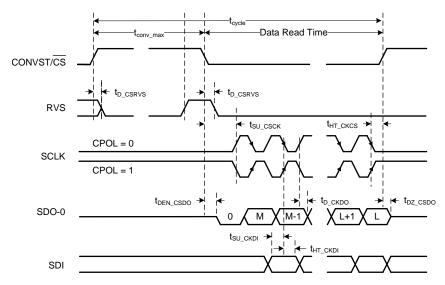

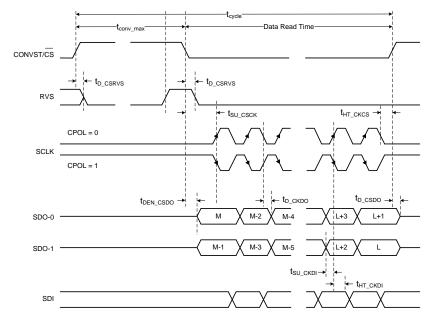

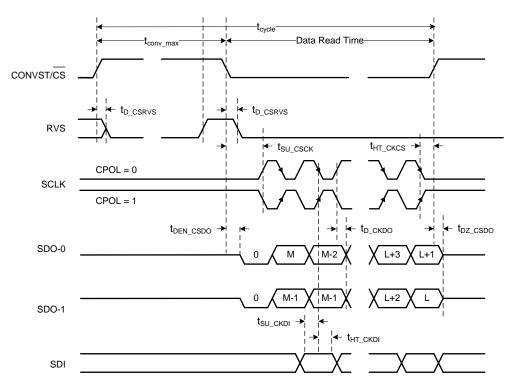

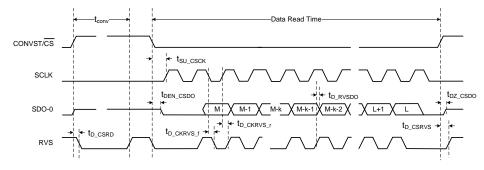

### 6.8 Timing Requirements: SPI-Compatible Serial Interface

all minimum and maximum specifications are at  $T_A = -40$ °C to +125°C; typical specifications are at  $T_A = 25$ °C; AVDD = 5 V, DVDD = 3.3 V,  $V_{REF} = 4.096$  V (internal), and maximum throughput (unless otherwise noted)

|                       |                                                              | MIN                | TYP MAX | UNIT             |

|-----------------------|--------------------------------------------------------------|--------------------|---------|------------------|

| TIMING RE             | QUIREMENTS                                                   |                    | ·       |                  |

| f <sub>CLK</sub>      | Serial clock frequency                                       |                    | 66.67   | MHz              |

| t <sub>CLK</sub>      | Serial clock time period                                     | 1/f <sub>CLK</sub> |         |                  |

| t <sub>PH_CK</sub>    | SCLK high time                                               | 0.45               | 0.55    | t <sub>CLK</sub> |

| t <sub>PL_CK</sub>    | SCLK low time                                                | 0.45               | 0.55    | t <sub>CLK</sub> |

| t <sub>SU_CSCK</sub>  | Setup time: CONVST/CS falling to first SCLK capture edge     | 7.5                |         | ns               |

| t <sub>SU_CKDI</sub>  | Setup time: SDI data valid to SCLK capture edge              | 7.5                |         | ns               |

| t <sub>HT_CKDI</sub>  | Hold time: SCLK capture edge to (previous) data valid on SDI | 7.5                |         | ns               |

| t <sub>HT_CKCS</sub>  | Delay time: last SCLK capture edge to CONVST/CS rising       | 7.5                |         | ns               |

| TIMING SPI            | ECIFICATIONS                                                 |                    |         |                  |

| t <sub>DEN_CSDO</sub> | Delay time: CONVST/CS falling edge to data enable            |                    | 9.5     | ns               |

| t <sub>DZ_CSDO</sub>  | Delay time: CONVST/CS rising to SDO-x going to 3-state       |                    | 10      | ns               |

| t <sub>D_CKDO</sub>   | Delay time: SCLK launch edge to (next) data valid on SDO-x   |                    | 12      | ns               |

| t <sub>D_CSRVS</sub>  | Delay time: CONVST/CS rising edge to RVS falling             |                    | 14      | ns               |

Product Folder Links: ADS8671 ADS8675

SBAS779 – DECEMBER 2016 www.ti.com

# 6.9 Timing Requirements: Source-Synchronous Serial Interface (External Clock)

all minimum and maximum specifications are at  $T_A = -40$ °C to +125°C; typical specifications are at  $T_A = 25$ °C; AVDD = 5 V, DVDD = 3.3 V,  $V_{REF} = 4.096$  V (internal), and maximum throughput (unless otherwise noted)

|                        |                                                                           | MIN                | TYP | MAX   | UNIT             |

|------------------------|---------------------------------------------------------------------------|--------------------|-----|-------|------------------|

| TIMING RE              | QUIREMENTS                                                                |                    |     | 1     |                  |

| f <sub>CLK</sub>       | Serial clock frequency                                                    |                    |     | 66.67 | MHz              |

| t <sub>CLK</sub>       | Serial clock time period                                                  | 1/f <sub>CLK</sub> |     |       |                  |

| t <sub>PH_CK</sub>     | SCLK high time                                                            | 0.45               |     | 0.55  | t <sub>CLK</sub> |

| t <sub>PL_CK</sub>     | SCLK low time                                                             | 0.45               |     | 0.55  | t <sub>CLK</sub> |

| TIMING SP              | ECIFICATIONS                                                              |                    |     |       |                  |

| t <sub>DEN_CSDO</sub>  | Delay time: CONVST/CS falling edge to data enable                         |                    |     | 9.5   | ns               |

| t <sub>DZ_CSDO</sub>   | Delay time: CONVST/CS rising to SDO-x going to 3-state                    |                    |     | 10    | ns               |

| t <sub>D_CKRVS_r</sub> | Delay time: SCLK rising edge to RVS rising                                |                    |     | 14    | ns               |

| t <sub>D_CKRVS_f</sub> | Delay time: SCLK falling edge to RVS falling                              |                    |     | 14    | ns               |

| t <sub>D_RVSDO</sub>   | Delay time: RVS rising to (next) data valid on SDO-x                      |                    |     | 2.5   | ns               |

| t <sub>D_CSRVS</sub>   | Delay time: CONVST/CS rising edge to RVS displaying internal device state |                    |     | 15    | ns               |

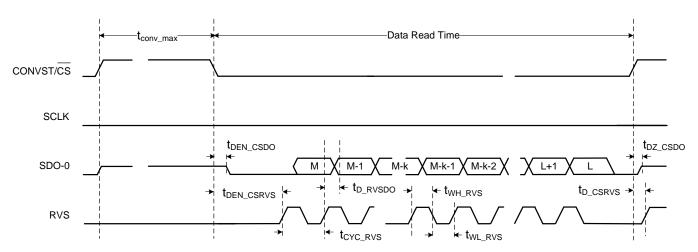

# 6.10 Timing Requirements: Source-Synchronous Serial Interface (Internal Clock)

all minimum and maximum specifications are at  $T_A = -40$ °C to +125°C; typical specifications are at  $T_A = 25$ °C; AVDD = 5 V, DVDD = 3.3 V,  $V_{REF} = 4.096$  V (internal), and maximum throughput (unless otherwise noted)

|                        |                                                                           | MIN | TYP | MAX | UNIT                |  |  |  |

|------------------------|---------------------------------------------------------------------------|-----|-----|-----|---------------------|--|--|--|

| TIMING SPECIFICATIONS  |                                                                           |     |     |     |                     |  |  |  |

| t <sub>DEN_CSDO</sub>  | Delay time: CONVST/CS falling edge to data enable                         |     |     | 9.5 | ns                  |  |  |  |

| t <sub>DZ_CSDO</sub>   | Delay time: CONVST/CS rising to SDO-x going to 3-state                    |     |     | 10  | ns                  |  |  |  |

| t <sub>DEN_CSRVS</sub> | Delay time: CONVST/CS falling edge to first rising edge on RVS            |     |     | 50  | ns                  |  |  |  |

| t <sub>D_RVSDO</sub>   | Delay time: RVS rising to (next) data valid on SDO-x                      |     |     | 2.5 | ns                  |  |  |  |

| t <sub>INTCLK</sub>    | Time period: internal clock                                               | 15  |     |     | ns                  |  |  |  |

| t <sub>CYC_RVS</sub>   | Time period: RVS signal                                                   | 15  |     |     | ns                  |  |  |  |

| t <sub>WH_RVS</sub>    | RVS high time                                                             | 0.4 |     | 0.6 | t <sub>INTCLK</sub> |  |  |  |

| t <sub>WL_RVS</sub>    | RVS low time                                                              | 0.4 |     | 0.6 | t <sub>INTCLK</sub> |  |  |  |

| t <sub>D_CSRVS</sub>   | Delay time: CONVST/CS rising edge to RVS displaying internal device state |     |     | 15  | ns                  |  |  |  |

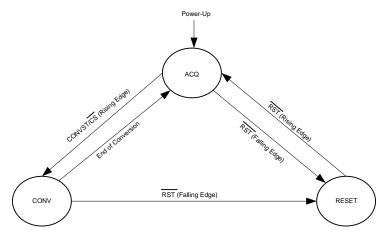

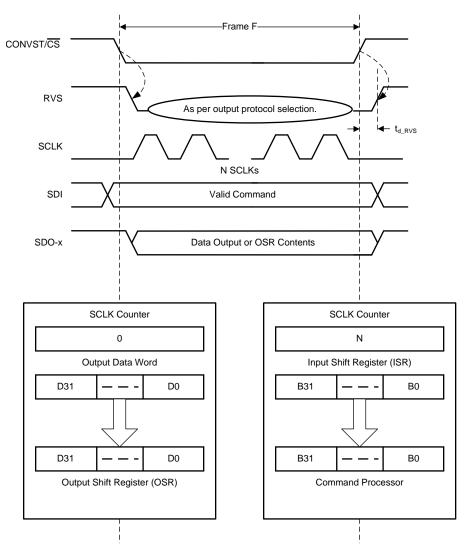

Figure 1. Conversion Cycle Timing Diagram

Figure 2. Asynchronous Reset Timing Diagram

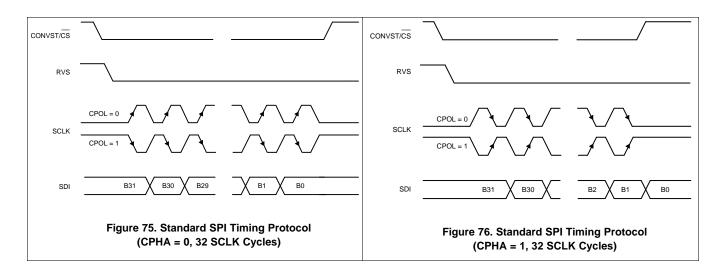

Figure 3. Standard SPI Interface Timing Diagram for CPHA = 0

Figure 4. Standard SPI Interface Timing Diagram for CPHA = 1

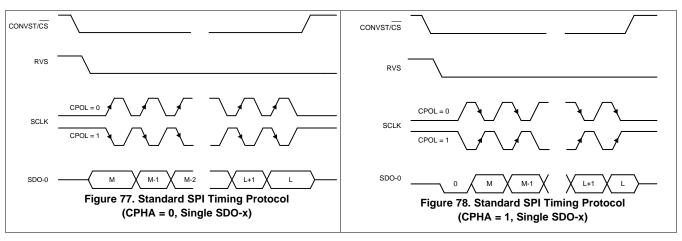

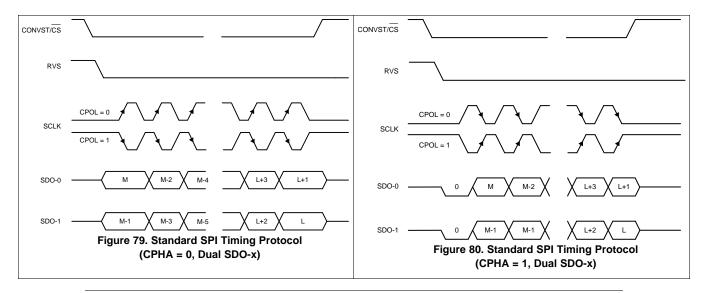

Figure 5. multiSPI Interface Timing Diagram for Dual SDO-x and CPHA = 0

Figure 6. multiSPI Interface Timing Diagram for Dual SDO-x and CPHA = 1

Figure 7. multiSPI Source-Synchronous External Clock Serial Interface Timing Diagram

Figure 8. multiSPI Source-Synchronous Internal Clock Serial Interface Timing Diagram

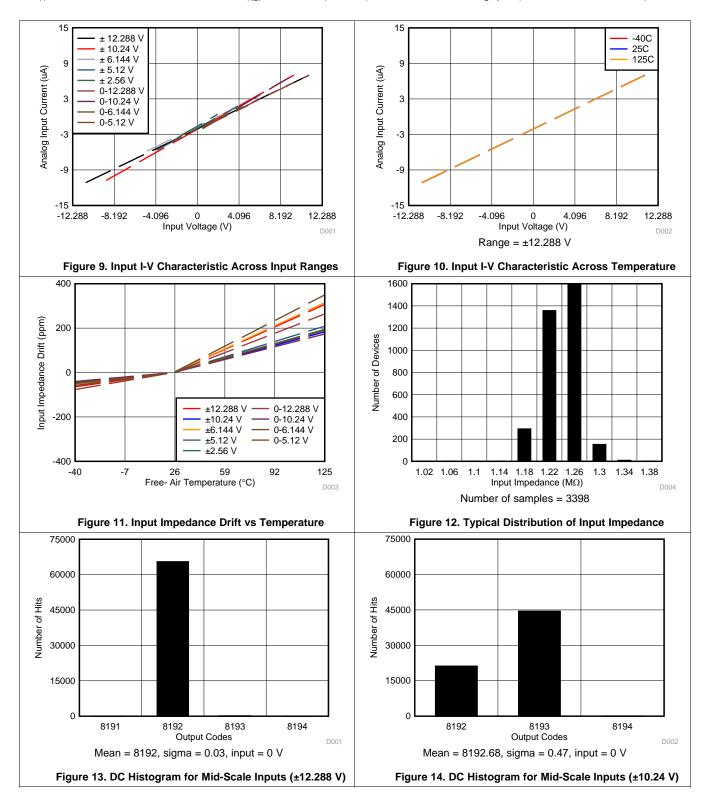

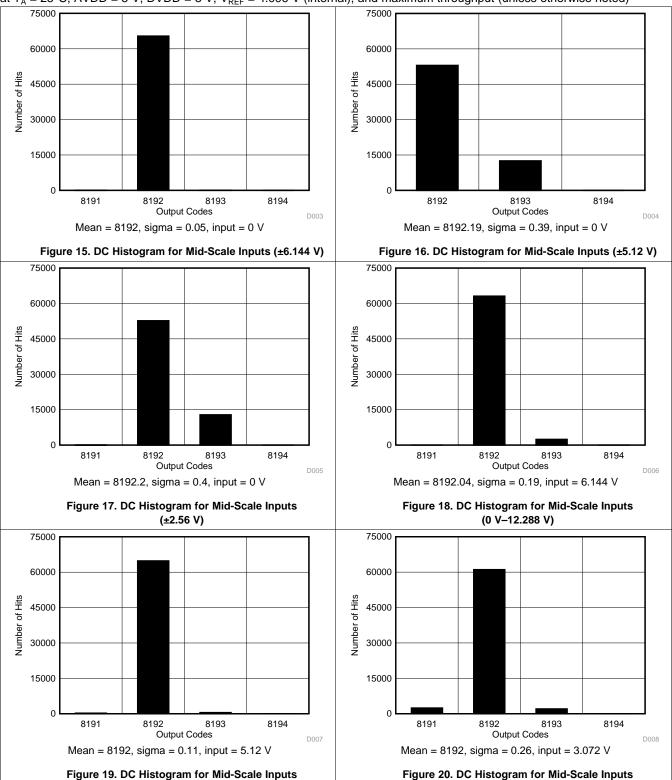

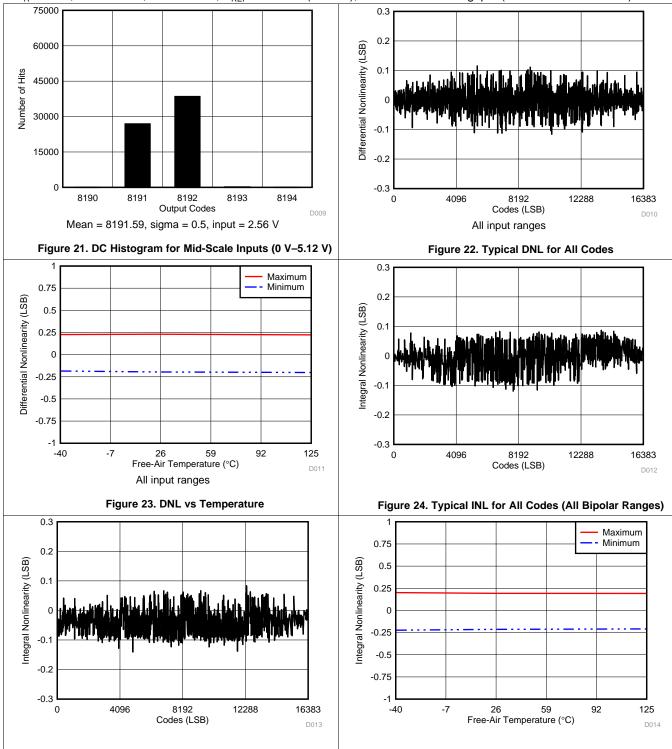

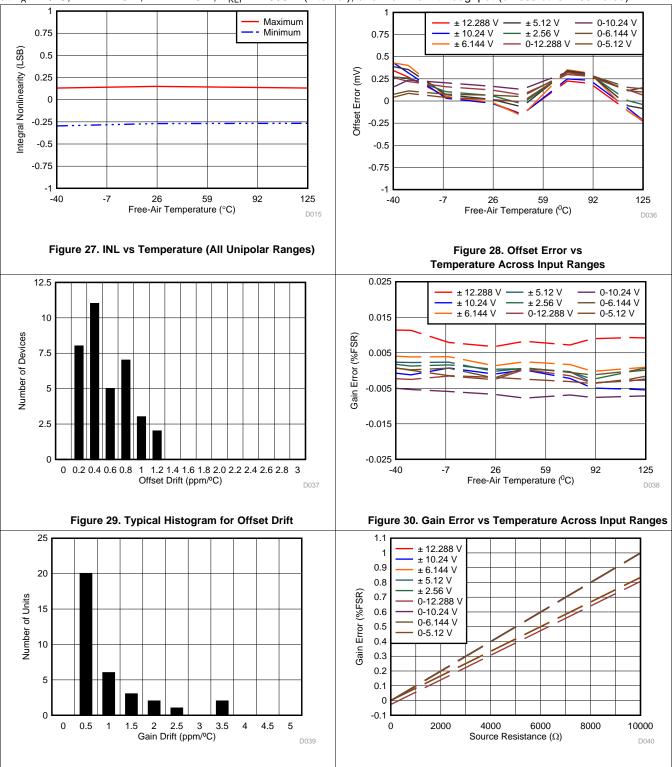

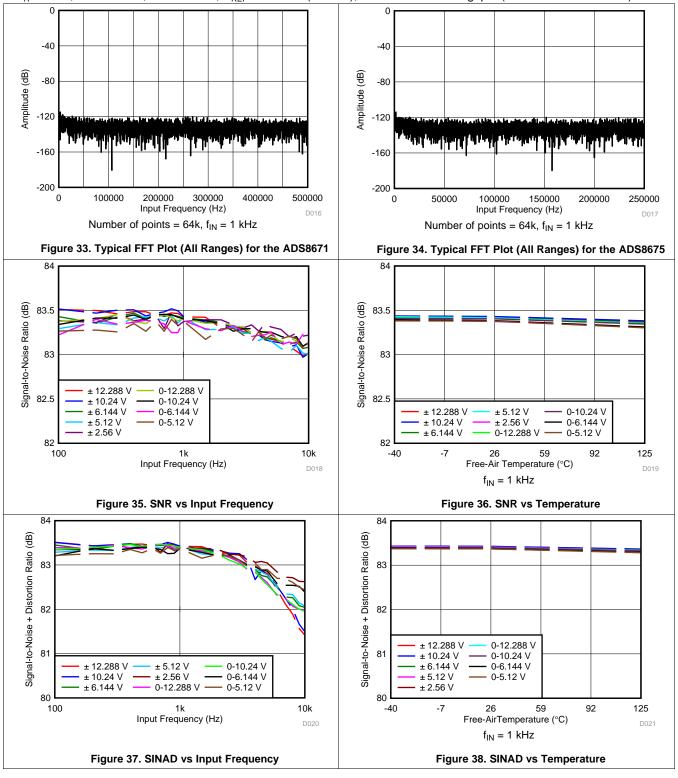

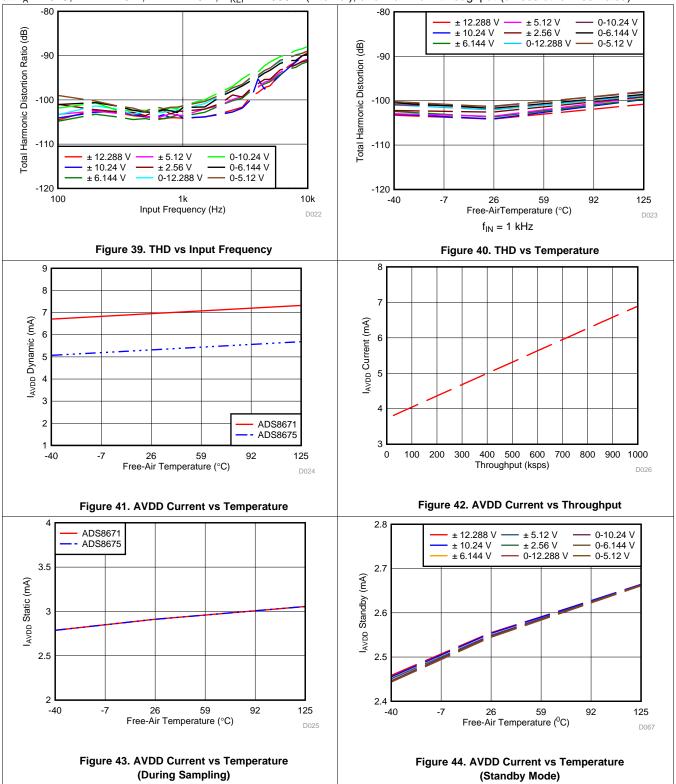

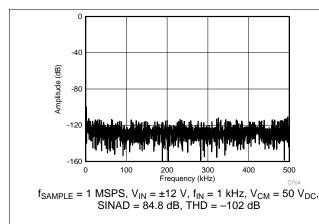

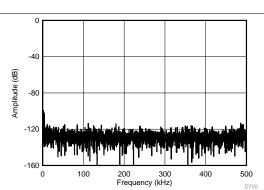

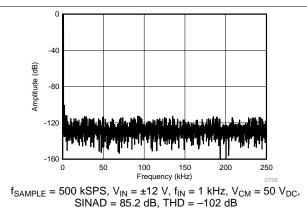

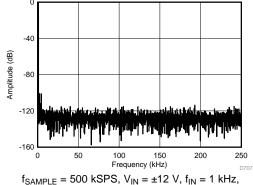

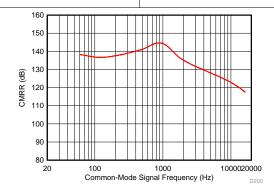

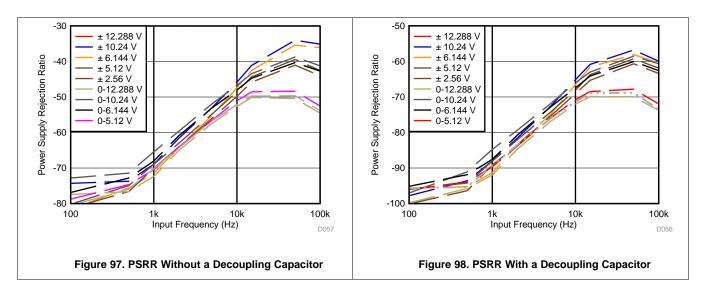

# 6.11 Typical Characteristics

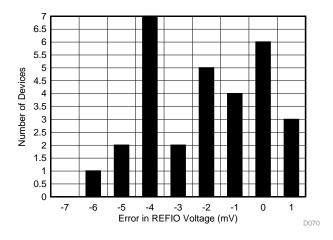

at T<sub>A</sub> = 25°C, AVDD = 5 V, DVDD = 3 V, V<sub>REF</sub> = 4.096 V (internal), and maximum throughput (unless otherwise noted)

**Typical Characteristics (continued)**

at T<sub>A</sub> = 25°C, AVDD = 5 V, DVDD = 3 V, V<sub>REF</sub> = 4.096 V (internal), and maximum throughput (unless otherwise noted)

(0 V-10.24 V)

(0 V-6.144 V)

# TEXAS INSTRUMENTS

# **Typical Characteristics (continued)**

at T<sub>A</sub> = 25°C, AVDD = 5 V, DVDD = 3 V, V<sub>REF</sub> = 4.096 V (internal), and maximum throughput (unless otherwise noted)

Figure 25. Typical INL for All Codes (All Unipolar Ranges)

Figure 26. INL vs Temperature (All Bipolar Ranges)

# **Typical Characteristics (continued)**

at  $T_A = 25$ °C, AVDD = 5 V, DVDD = 3 V,  $V_{REF} = 4.096$  V (internal), and maximum throughput (unless otherwise noted)

Figure 31. Typical Histogram for Gain Error Drift

Figure 32. Gain Error vs External Resistance (R<sub>FXT</sub>)

# TEXAS INSTRUMENTS

# **Typical Characteristics (continued)**

at T<sub>A</sub> = 25°C, AVDD = 5 V, DVDD = 3 V, V<sub>REF</sub> = 4.096 V (internal), and maximum throughput (unless otherwise noted)

# **Typical Characteristics (continued)**

at  $T_A = 25$ °C, AVDD = 5 V, DVDD = 3 V,  $V_{REF} = 4.096$  V (internal), and maximum throughput (unless otherwise noted)

SBAS779 – DECEMBER 2016 www.ti.com

# TEXAS INSTRUMENTS

# **Typical Characteristics (continued)**

at  $T_A = 25$ °C, AVDD = 5 V, DVDD = 3 V,  $V_{REF} = 4.096$  V (internal), and maximum throughput (unless otherwise noted)

# 7 Detailed Description

#### 7.1 Overview

The ADS867x devices belong to a family of high-speed, high-performance, easy-to-use integrated data acquisition system. This single-channel device supports true bipolar input voltage swings up to ±12.288 V, operating on a single 5-V analog supply. The device features an enhanced SPI interface (multiSPI) that allows the sampling rate to be maximized even with lower speed host controllers.

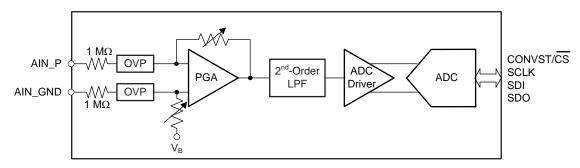

The device consists of a high-precision successive approximation register (SAR) analog-to-digital converter (ADC) and a power-optimized analog front-end (AFE) circuit for signal conditioning that includes:

- A high-resistive input impedance (≥ 1 MΩ) that is independent of the sampling rate

- A programmable gain amplifier (PGA) with a pseudo-differential input configuration supporting nine softwareprogrammable unipolar and bipolar input ranges

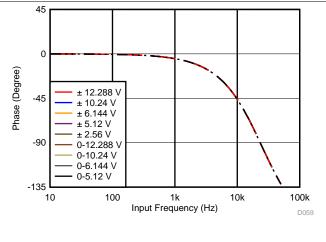

- · A second-order, low-pass antialiasing filter

- An ADC driver amplifier that ensures quick settling of the SAR ADC input for high accuracy

- An input overvoltage protection circuit up to ±20 V

The device also features a low temperature drift, 4.096-V internal reference with a fast-settling buffer and a multiSPI serial interface with daisy-chain (DAISY) and ALARM features.

The integration of the multichannel precision AFE circuit with high input impedance and a precision ADC operating from a single 5-V supply offers a simplified end solution without requiring external high-voltage bipolar supplies and complicated driver circuits.

#### 7.2 Functional Block Diagram

# INSTRUMENTS

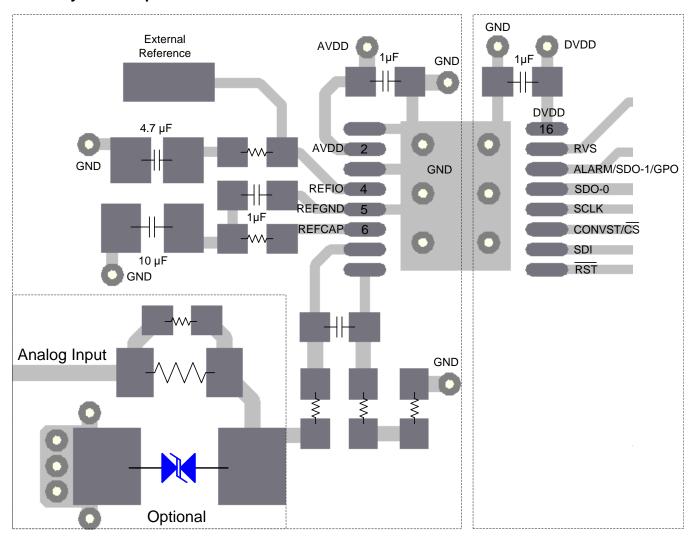

#### 7.3 Feature Description

### 7.3.1 Analog Input Structure

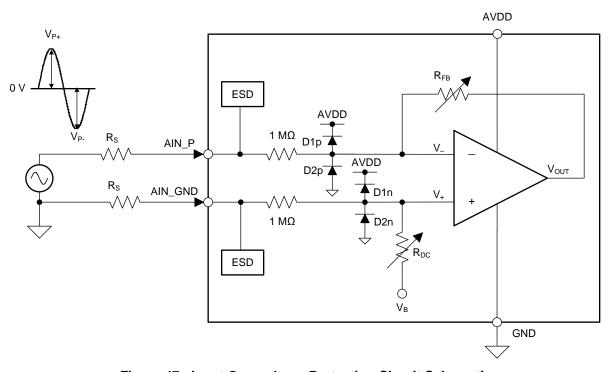

The device features a pseudo-differential input structure, meaning that the single-ended analog input signal is applied at the positive input AIN P and the negative input AIN GND is tied to GND. Figure 46 shows the simplified circuit schematic for the AFE circuit, including the input overvoltage protection circuit, PGA, low-pass filter (LPF), and high-speed ADC driver.

Figure 46. Simplified Analog Front-End Circuit Schematic

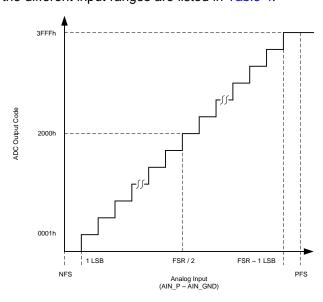

The device can support multiple unipolar or bipolar, single-ended input voltage ranges based on the configuration of the program registers. As explained in the RANGE\_SEL\_REG register, the input voltage range for each analog channel can be configured to bipolar ±3 x V<sub>REF</sub>, ±2.5 x V<sub>REF</sub>, ±1.5 x V<sub>REF</sub>, ±1.25 x V<sub>REF</sub>, and ±0.625 x  $V_{REF}$  or unipolar 0 to 3 x  $V_{REF}$ , 0 to 2.5 x  $V_{REF}$ , 0 to 1.5 x  $V_{REF}$  and 0 to 1.25 x  $V_{REF}$ . With the internal or external reference voltage set to 4.096 V, the input ranges of the device can be configured to bipolar ranges of ±12.288 V, ±10.24 V, ±6.144 V, ±5.12 V, and ±2.56 V or unipolar ranges of 0 V to 12.288 V, 0 V to 10.24 V, 0 V to 6.144 V, and 0 V to 5.12 V.

The device samples the voltage difference (AIN\_P - AIN\_GND) between the analog input and the AIN\_GND pin. The device allows a ±0.1-V range on the AIN GND pin. This feature is useful in modular systems where the sensor or signal-conditioning block is further away from the ADC on the board and when a difference in the ground potential of the sensor or signal conditioner from the ADC ground is possible. In such cases, running separate wires from the AIN GND pin of the device to the sensor or signal-conditioning ground is recommended. In order to obtain optimum performance, the input currents and impedances along each input path are recommended to be matched. The two single-ended signals to AIN\_P and AIN\_GND must be routed as symmetrically as possible from the signal source to the ADC input pins.

If the analog input pin (AIN P) to the device is left floating, the output of the ADC corresponds to an internal biasing voltage. The output from the ADC must be considered as invalid if the device is operated with floating input pins. This condition does not cause any damage to the device, which becomes fully functional when a valid input voltage is applied to the pins.

#### 7.3.2 Analog Input Impedance

The device presents a resistive input impedance  $\geq 1 \text{ M}\Omega$  on each of the analog inputs. The input impedance is independent of the ADC sampling frequency or the input signal frequency. The primary advantage of such highimpedance inputs is the ease of driving the ADC inputs without requiring driving amplifiers with low output impedance. Bipolar, high-voltage power supplies are not required in the system because this ADC does not require any high-voltage, front-end drivers. In most applications, the signal sources or sensor outputs can be directly connected to the ADC input, thus significantly simplifying the design of the signal chain.

In order to maintain the dc accuracy of the system, matching the external source impedance on the AIN\_P input pin with an equivalent resistance on the AIN\_GND pin is recommended. This matching helps cancel any additional offset error contributed by the external resistance.

### **Feature Description (continued)**

### 7.3.3 Input Protection Circuit

The device features an internal overvoltage protection (OVP) circuit on each of the analog inputs. Use the internal protection circuit only as a secondary protection scheme. The external protection devices in the end application are highly recommended to be used to protect against surges, electrostatic discharge (ESD), and electrical fast transient (EFT) conditions. A conceptual block diagram of the internal OVP circuit is shown in Figure 47.

Figure 47. Input Overvoltage Protection Circuit Schematic

As shown in Figure 47, the combination of the 1-M $\Omega$  (or, 1.2 M $\Omega$  for appropriate input ranges) input resistors along with the PGA gain-setting resistors R<sub>FB</sub> and R<sub>DC</sub> limit the current flowing into the input pin. A combination of anti-parallel diodes, D1 and D2 are added to protect the internal circuitry and set the overvoltage protection limits.

Table 1 explains the various operating conditions for the device when powered on. This table indicates that when the device is properly powered up (AVDD = 5 V) or offers a low impedance of < 30 k $\Omega$ , the internal overvoltage protection circuit can withstand up to ±20 V on the analog input pins.

Table 1. Input Overvoltage Protection Limits When AVDD = 5 V or Offers a Low Impedance of < 30 k $\Omega^{(1)}$

| INPUT<br>(V <sub>ov</sub>               | TEST<br>CONDITION                                   | ADC<br>OUTPUT    | COMMENTS  |                                                                                                  |

|-----------------------------------------|-----------------------------------------------------|------------------|-----------|--------------------------------------------------------------------------------------------------|

| CONDITION                               | RANGE                                               | CONDITION        | OUIPUI    |                                                                                                  |

| V <sub>IN</sub>   <  V <sub>RANGE</sub> | Within operating range                              | All input ranges | Valid     | Device functions as per data sheet specifications.                                               |

| $ V_{RANGE}  <  V_{IN}  <  V_{OVP} $    | Beyond operating range but within overvoltage range | All input ranges | Saturated | ADC output is saturated, but device is internally protected (not recommended for extended time). |

| $ V_{IN}  >  V_{OVP} $                  | Beyond overvoltage range                            | All input ranges | Saturated | This usage condition can cause irreversible damage to the device.                                |

(1) GND = 0 V, AIN\_GND = 0 V,  $|V_{RANGE}|$  is the maximum input voltage for any selected input range, and  $|V_{OVP}|$  is the break-down voltage for the internal OVP circuit. Assume that  $R_S$  is approximately 0  $\Omega$ .

The results indicated in Table 1 are based on an assumption that the analog input pin is driven by a very low impedance source ( $R_S$  is approximately 0  $\Omega$ ). However, if the source driving the input has higher impedance, the current flowing through the protection diodes reduces further, thereby increasing the OVP voltage range. Note that higher source impedances result in gain errors and contribute to overall system noise performance.

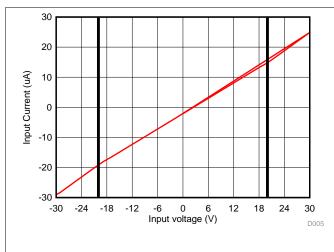

Figure 48 shows the voltage versus current response of the internal overvoltage protection circuit when the device is powered on. According to this current-to-voltage (I-V) response, the current flowing into the device input pin is limited by the 1-M $\Omega$  (or 1.2 M $\Omega$  for appropriate input ranges) input impedance. However, for voltages beyond ±20 V, the internal node voltages surpass the break-down voltage for internal transistors, thus setting the limit for overvoltage protection on the input pin.

The same overvoltage protection circuit also provides protection to the device when the device is not powered on and AVDD is floating with an impedance > 30 k $\Omega$ . This condition can arise when the input signals are applied before the ADC is fully powered on. The overvoltage protection limits for this condition are shown in Table 2.

Table 2. Input Overvoltage Protection Limits When AVDD = Floating with Impedance > 30 k $\Omega^{(1)}$

| INPUT CONDITION<br>(V <sub>OVP</sub> = ±11 V) |                          | TEST ADC OUTPUT  |         | COMMENTS                                                                 |  |

|-----------------------------------------------|--------------------------|------------------|---------|--------------------------------------------------------------------------|--|

| CONDITION                                     | RANGE                    | CONDITION        |         |                                                                          |  |

| $ V_{IN}  <  V_{OVP} $                        | Within overvoltage range | All input ranges | Invalid | Device is not functional but is protected internally by the OVP circuit. |  |

| $ V_{IN}  >  V_{OVP} $                        | Beyond overvoltage range | All input ranges | Invalid | This usage condition can cause irreversible damage to the device.        |  |

AVDD = floating, GND = 0 V, AIN\_GND = 0 V,  $|V_{RANGE}|$  is the maximum input voltage for any selected input range, and  $|V_{OVP}|$  is the break-down voltage for the internal OVP circuit. Assume that  $R_S$  is approximately 0  $\Omega$ .

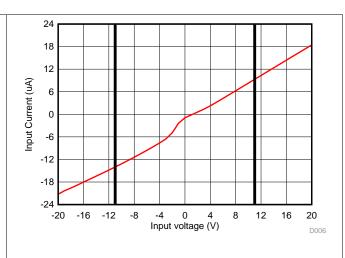

Figure 49 shows the I-V response of the internal overvoltage protection circuit when the device is not powered on. According to this I-V response, the current flowing into the device input pin is limited by the 1-M $\Omega$  input impedance. However, for voltages beyond ±11 V, the internal node voltage surpasses the break-down voltage for internal transistors, thus setting the limit for overvoltage protection on the input pin.

Figure 48. I-V Curve for the Input OVP Circuit (AVDD = 5 V)

Figure 49. I-V Curve for the Input OVP Circuit (AVDD = Floating)

Copyright © 2016, Texas Instruments Incorporated

### 7.3.4 Programmable Gain Amplifier (PGA)

The device features a programmable gain amplifier (PGA) as part of the analog signal-conditioning circuit that converts the original single-ended input signal into a fully-differential signal to drive the internal SAR ADC. The PGA also adjusts the common-mode level of the input signal before feeding it into the SAR ADC to ensure maximum usage of the ADC input dynamic range. Depending on the range of the input signal, the PGA gain can be adjusted by setting the RANGE\_SEL[3:0] bits in the configuration register (see the RANGE\_SEL\_REG register). The default or power-on state for the RANGE\_SEL[3:0] bits is 0000, corresponding to an input signal range of ±3 x V<sub>REF</sub>. Table 3 lists the various configurations of the RANGE\_SEL[3:0] bits for the different analog input voltage ranges.

The PGA uses a precisely-matched network of resistors for multiple gain configurations. Matching between these resistors is accurately trimmed to keep the overall gain error low across all input ranges.

| ANALOG INPUT RANGE        | RANGE_SEL[3:0] |       |       |       |  |

|---------------------------|----------------|-------|-------|-------|--|

| ANALOG INPUT KANGE        | BIT 3          | BIT 2 | BIT 1 | BIT 0 |  |

| ±3 × V <sub>REF</sub>     | 0              | 0     | 0     | 0     |  |

| ±2.5 × V <sub>REF</sub>   | 0              | 0     | 0     | 1     |  |

| ±1.5 × V <sub>REF</sub>   | 0              | 0     | 1     | 0     |  |

| ±1.25 × V <sub>REF</sub>  | 0              | 0     | 1     | 1     |  |